Contents

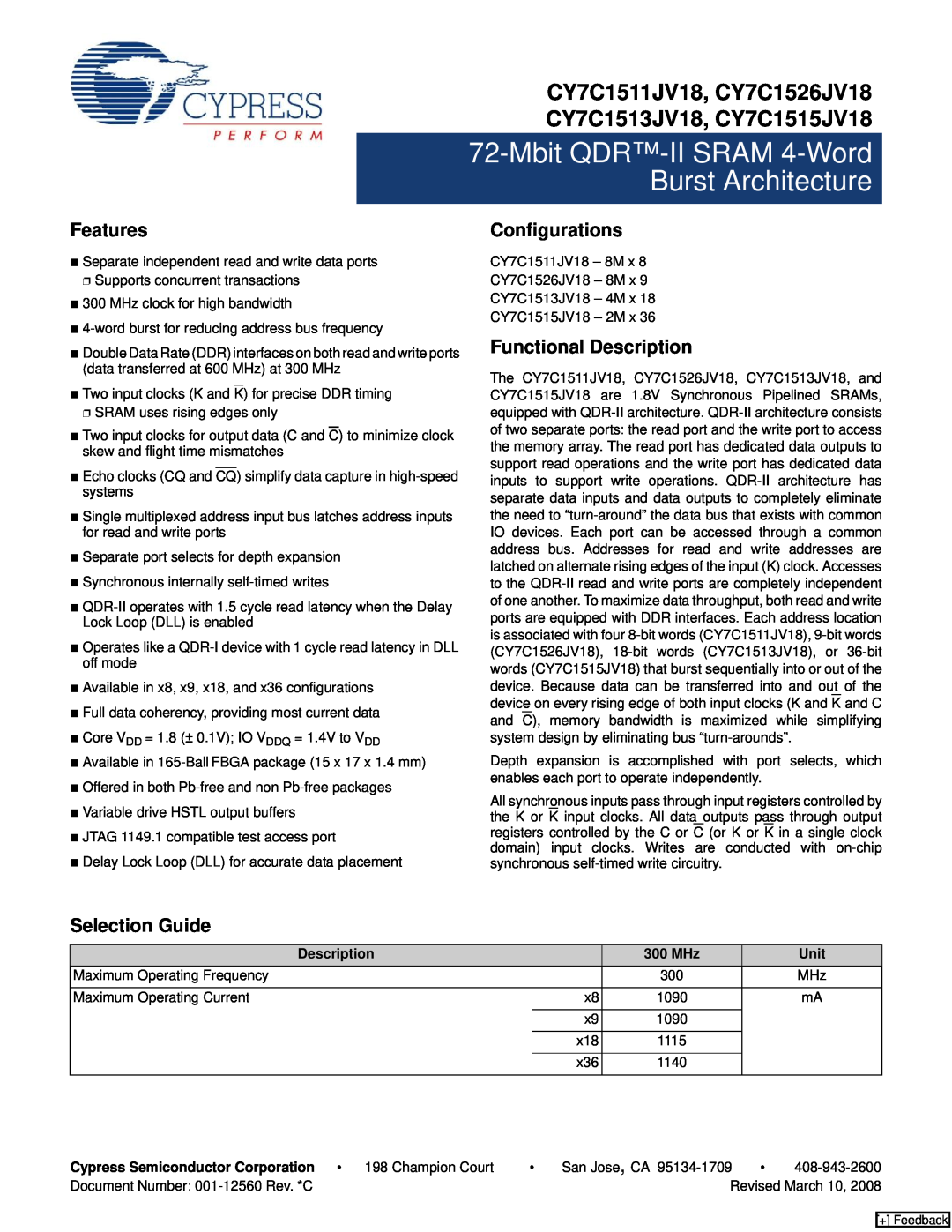

Configurations

Features

CY7C1511JV18, CY7C1526JV18 CY7C1513JV18, CY7C1515JV18

Functional Description

Logic Block Diagram CY7C1526JV18

Logic Block Diagram CY7C1511JV18

CY7C1511JV18, CY7C1526JV18 CY7C1513JV18, CY7C1515JV18

Logic Block Diagram CY7C1515JV18

Logic Block Diagram CY7C1513JV18

165-Ball FBGA 15 x 17 x 1.4 mm Pinout

Pin Configuration

CY7C1511JV18, CY7C1526JV18 CY7C1513JV18, CY7C1515JV18

CY7C1513JV18, CY7C1515JV18

CY7C1511JV18, CY7C1526JV18

Pin Definitions

Pin Definitions continued

CY7C1513JV18, CY7C1515JV18

Read Operations

Functional Overview

Write Operations

Byte Write Operations

Depth Expansion

Concurrent Transactions

Programmable Impedance

Echo Clocks

Application Example

CY7C1511JV18, CY7C1526JV18

Truth Table

ASIC

Write Cycle Descriptions

Write Cycle Descriptions

Test Access Port-Test Clock

Disabling the JTAG Feature

Performing a TAP Reset

IEEE 1149.1 Serial Boundary Scan JTAG

SAMPLE Z

IDCODE

SAMPLE/PRELOAD

BYPASS

Page 15 of

TAP Controller State Diagram

TAP Electrical Characteristics

TAP Controller Block Diagram

TAP Timing and Test Conditions

TAP AC Switching Characteristics

Scan Register Sizes

Identification Register Definitions

Instruction Codes

CY7C1511JV18

Boundary Scan Order

Power Up Waveforms

Power Up Sequence in QDR-II SRAM

Power Up Sequence

DLL Constraints

DC Electrical Characteristics

Electrical Characteristics

AC Electrical Characteristics

Maximum Ratings

Thermal Resistance

Capacitance

AC Test Loads and Waveforms

Package

Parameter

Switching Characteristics

READ

Switching Waveforms

WRITE

K K RPS WPS

Ordering Information

Figure 4. 165-ball FBGA 15 x 17 x 1.40 mm

Package Diagram

ISSUE

Document History Page

Burst Architecture Document Number

ECN NO