64 Kbit (8K x 8) AutoStore nvSRAM

Features

■35 ns and 55 ns access times

■Hands off automatic STORE on power down with external 68 µF capacitor

■STORE to QuantumTrap™ nonvolatile elements is initiated by software, hardware, or AutoStore™ on power down

■RECALL to SRAM initiated by software or power up

■Unlimited Read, Write, and Recall cycles

■1,000,000 STORE cycles to QuantumTrap

■100 year data retention to QuantumTrap

■Single 5V+10% operation

■Military temperature

■

Functional Description

The Cypress

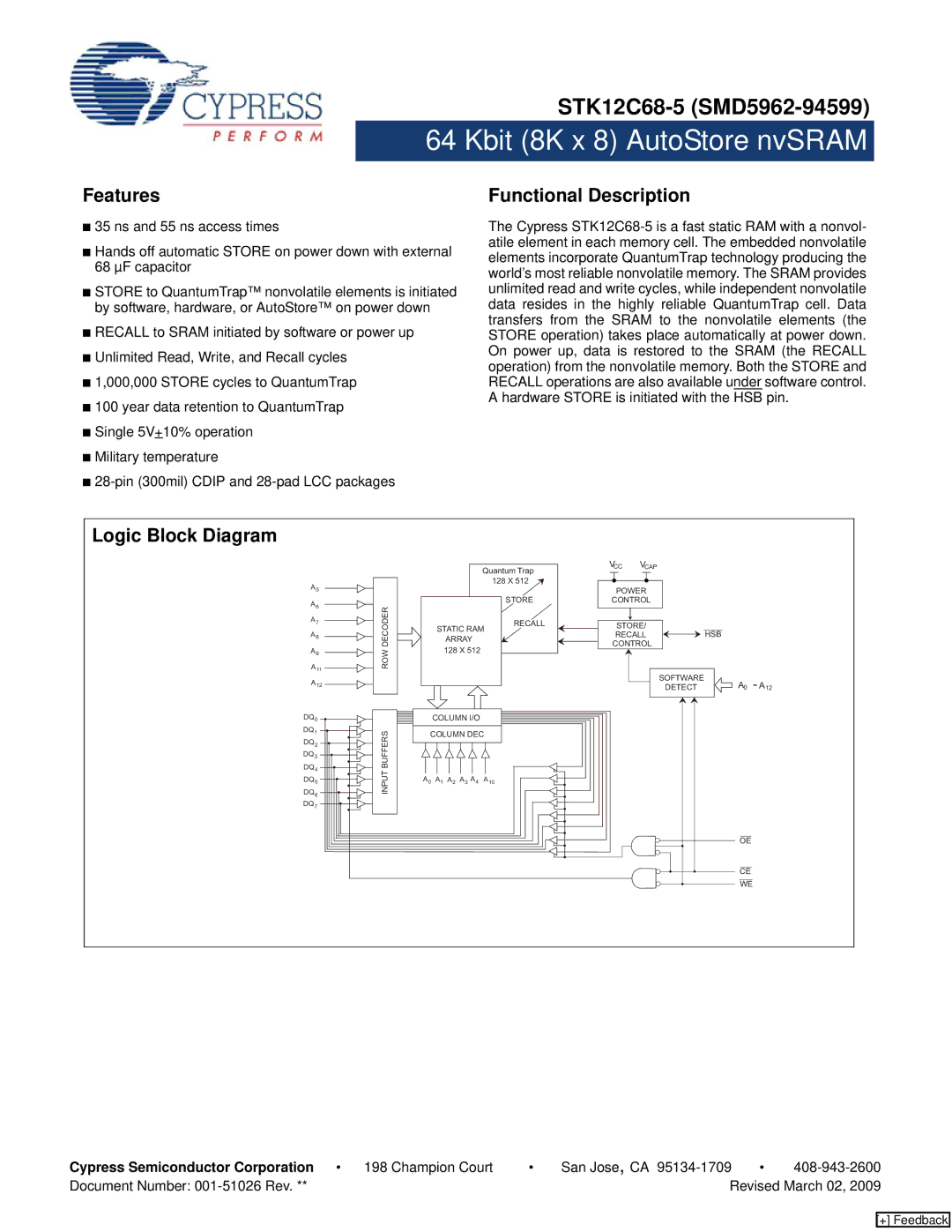

Logic Block Diagram

A5

A6

Quantum Trap

128 X 512

STORE

VCC VCAP

POWER |

CONTROL |

A7

A8

A9

A11 A12

ROW DECODER

STATIC RAM

ARRAY

128 X 512

RECALL

| STORE/ |

|

|

|

|

|

| ||

| RECALL |

|

|

|

|

|

| ||

|

|

|

| HSB | |||||

|

|

|

| ||||||

| CONTROL |

|

|

|

|

|

| ||

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

| SOFTWARE |

|

| A0 - A12 | |||

|

|

|

| DETECT |

|

| |||

DQ0 DQ1 DQ2 DQ3 DQ4 DQ5 DQ6 DQ7

COLUMN I/O

BUFFERS |

| COLUMN DEC |

|

| |

INPUT | A | 0 A1 A2 A3 A4 A10 |

|

|

OE

CE

WE

Cypress Semiconductor Corporation • 198 Champion Court | • | San Jose, CA | • | |

Document Number: |

| Revised March 02, 2009 | ||

[+] Feedback