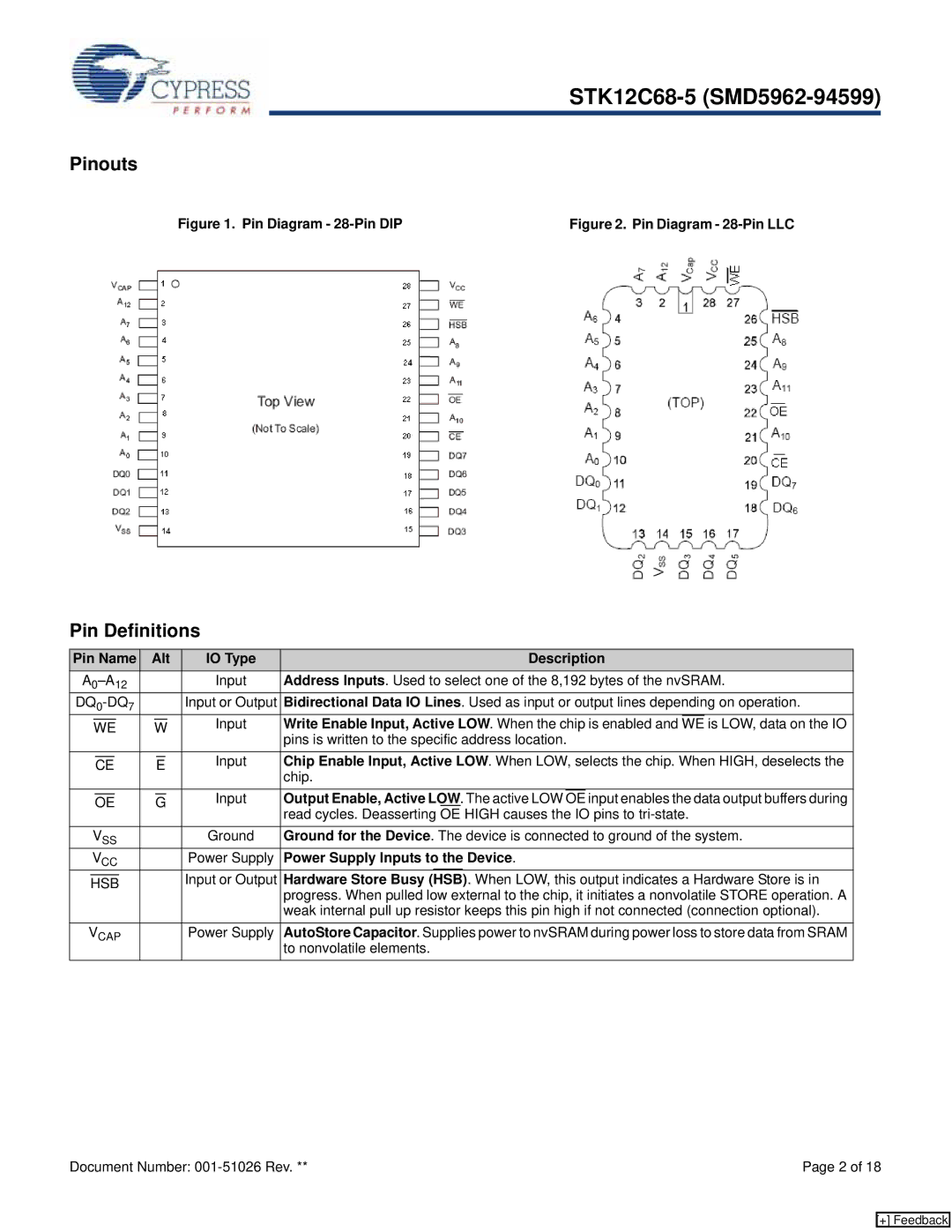

Pinouts

Figure 1. Pin Diagram - | Figure 2. Pin Diagram - |

Pin Definitions

Pin Name | Alt | IO Type |

|

| Description | |||||||||||||||||

|

|

|

|

|

|

| Input | Address Inputs. Used to select one of the 8,192 bytes of the nvSRAM. | ||||||||||||||

|

|

|

|

|

|

| Input or Output | Bidirectional Data IO Lines. Used as input or output lines depending on operation. | ||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Input | Write Enable Input, Active LOW. When the chip is enabled and | WE | is LOW, data on the IO | ||||

|

| WE | W | |||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| pins is written to the specific address location. | ||||||

|

|

|

|

|

|

|

|

|

|

|

|

| Input | Chip Enable Input, Active LOW. When LOW, selects the chip. When HIGH, deselects the | ||||||||

|

|

| CE |

| E | |||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| chip. | ||||||

|

|

|

|

|

|

|

|

|

|

|

|

| Input | Output Enable, Active LOW. The active LOW | OE | input enables the data output buffers during | ||||||

|

| OE |

| G | ||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| read cycles. Deasserting OE HIGH causes the IO pins to | ||||||

| VSS |

|

|

|

|

|

|

| Ground | Ground for the Device. The device is connected to ground of the system. | ||||||||||||

| VCC |

|

|

|

|

|

|

| Power Supply | Power Supply Inputs to the Device. | ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Input or Output | Hardware Store Busy | (HSB) | . When LOW, this output indicates a Hardware Store is in | ||||

| HSB |

|

|

|

|

|

|

| ||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| progress. When pulled low external to the chip, it initiates a nonvolatile STORE operation. A | ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| weak internal pull up resistor keeps this pin high if not connected (connection optional). | ||||||

VCAP |

|

|

|

|

|

|

| Power Supply | AutoStore Capacitor. Supplies power to nvSRAM during power loss to store data from SRAM | |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| to nonvolatile elements. | ||||||

Document Number: | Page 2 of 18 |

[+] Feedback