STK17TA8

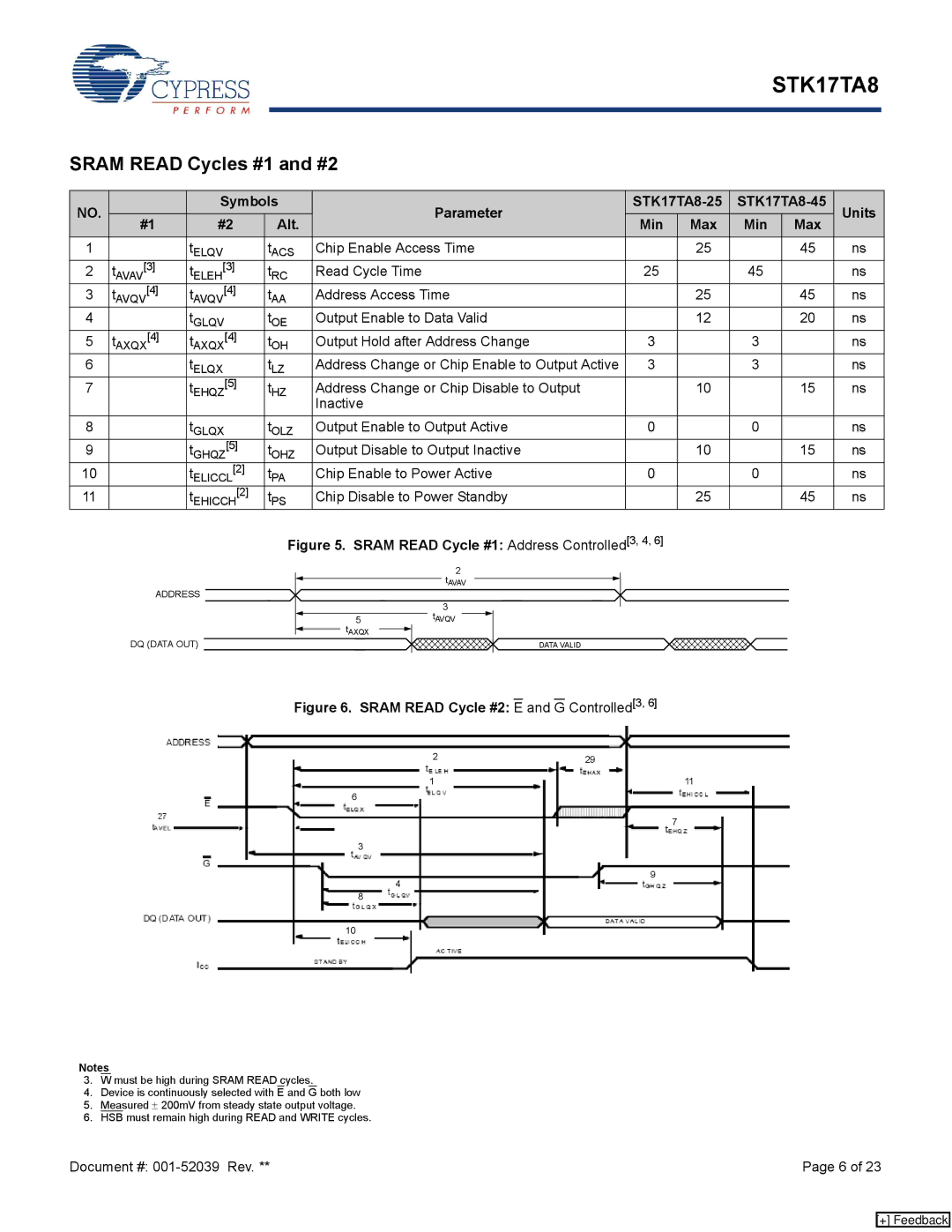

SRAM READ Cycles #1 and #2

NO. |

| Symbols | Parameter |

|

| Units | ||||

#1 | #2 | Alt. | Min | Max | Min | Max | ||||

|

|

| ||||||||

1 |

| tELQV | tACS | Chip Enable Access Time |

| 25 |

| 45 | ns | |

2 | tAVAV[3] | tELEH[3] | tRC | Read Cycle Time | 25 |

| 45 |

| ns | |

3 | tAVQV[4] | tAVQV[4] | tAA | Address Access Time |

| 25 |

| 45 | ns | |

4 |

| tGLQV | tOE | Output Enable to Data Valid |

| 12 |

| 20 | ns | |

5 | tAXQX[4] | tAXQX[4] | tOH | Output Hold after Address Change | 3 |

| 3 |

| ns | |

6 |

| tELQX | tLZ | Address Change or Chip Enable to Output Active | 3 |

| 3 |

| ns | |

7 |

| tEHQZ[5] | tHZ | Address Change or Chip Disable to Output |

| 10 |

| 15 | ns | |

|

|

|

| Inactive |

|

|

|

|

| |

8 |

| tGLQX | tOLZ | Output Enable to Output Active | 0 |

| 0 |

| ns | |

9 |

| tGHQZ[5] | tOHZ | Output Disable to Output Inactive |

| 10 |

| 15 | ns | |

10 |

| tELICCL[2] | tPA | Chip Enable to Power Active | 0 |

| 0 |

| ns | |

11 |

| tEHICCH[2] | tPS | Chip Disable to Power Standby |

| 25 |

| 45 | ns | |

Figure 5. SRAM READ Cycle #1: Address Controlled[3, 4, 6]

ADDRESS

DQ (DATA OUT)

2

tAVAV

3

5tAVQV

tAXQX ![]()

![]()

DATA VALID

Figure 6. SRAM READ Cycle #2: E and G Controlled[3, 6]

2 | 29 |

1 | 11 |

6

7

3

9

4

8

10

Notes

3.W must be high during SRAM READ cycles.

4.Device is continuously selected with E and G both low

5.Measured ± 200mV from steady state output voltage.

6.HSB must remain high during READ and WRITE cycles.

Document #: | Page 6 of 23 |

[+] Feedback