|

|

|

|

|

|

|

|

|

|

|

| STK17TA8 | |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

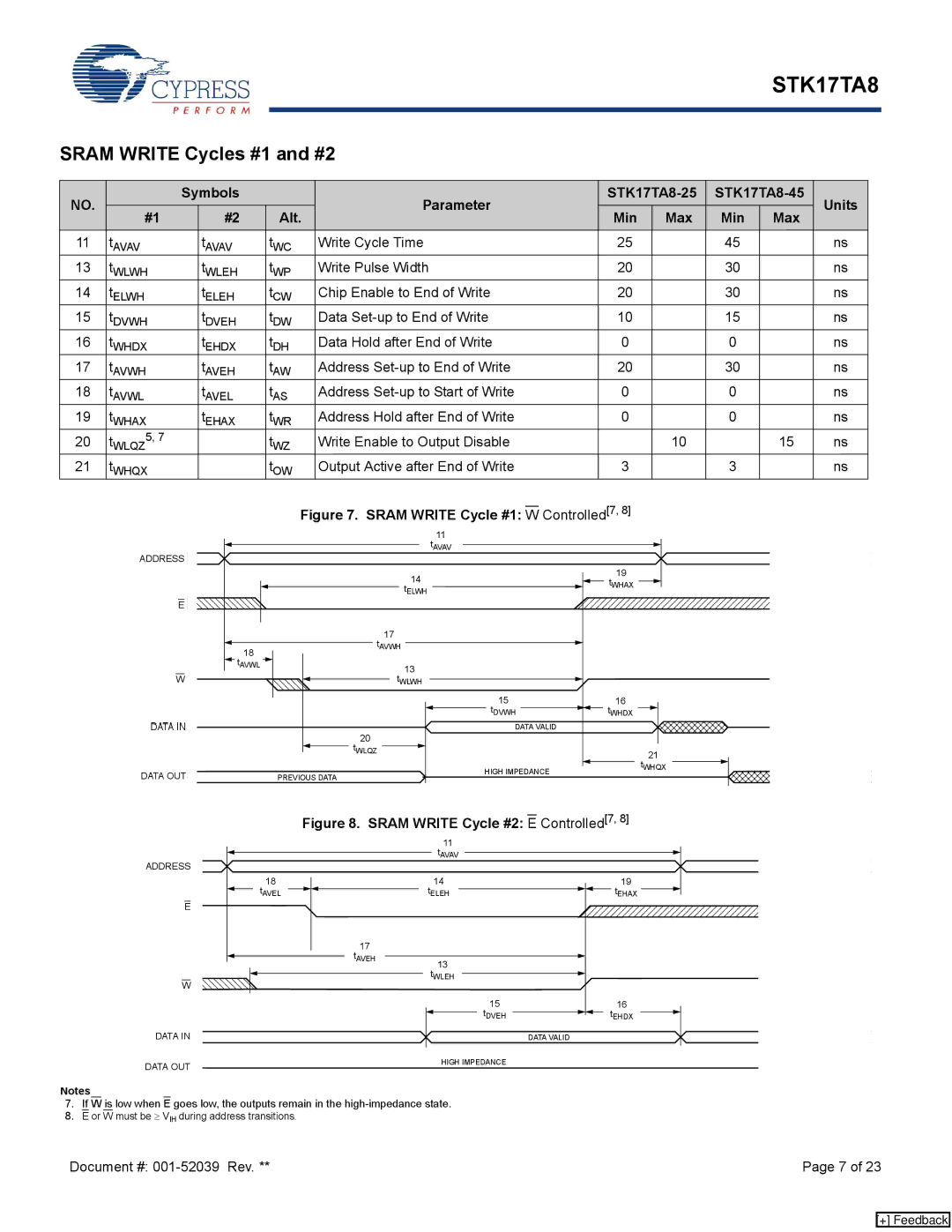

SRAM WRITE Cycles #1 and #2 |

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| NO. |

| Symbols |

|

| Parameter | Units |

|

| ||||||

| #1 |

| #2 |

|

| Alt. | Min | Max | Min | Max |

|

| |||

|

|

|

|

|

|

|

|

| |||||||

11 | tAVAV |

| tAVAV |

| tWC | Write Cycle Time | 25 |

| 45 |

| ns |

|

| ||

13 | tWLWH |

| tWLEH |

| tWP | Write Pulse Width | 20 |

| 30 |

| ns |

|

| ||

14 | tELWH |

| tELEH |

| tCW | Chip Enable to End of Write | 20 |

| 30 |

| ns |

|

| ||

15 | tDVWH |

| tDVEH |

| tDW | Data | 10 |

| 15 |

| ns |

|

| ||

16 | tWHDX |

| tEHDX |

| tDH | Data Hold after End of Write | 0 |

| 0 |

| ns |

|

| ||

17 | tAVWH |

| tAVEH |

| tAW | Address | 20 |

| 30 |

| ns |

|

| ||

18 | tAVWL |

| tAVEL |

| tAS | Address | 0 |

| 0 |

| ns |

|

| ||

19 | tWHAX |

| tEHAX |

| tWR | Address Hold after End of Write | 0 |

| 0 |

| ns |

|

| ||

20 | tWLQZ5, 7 |

|

|

| tWZ | Write Enable to Output Disable |

| 10 |

| 15 | ns |

|

| ||

21 | tWHQX |

|

|

| tOW | Output Active after End of Write | 3 |

| 3 |

| ns |

|

| ||

Figure 7. SRAM WRITE Cycle #1: W Controlled[7, 8]

|

|

| 11 |

|

|

|

| tAVAV |

|

ADDRESS |

|

|

|

|

|

|

| 14 | 19 |

|

|

| tWHAX | |

|

|

| tELWH |

|

E |

|

|

|

|

|

|

| 17 |

|

| 18 |

| tAVWH |

|

| tAVWL |

| 13 |

|

W |

|

| tWLWH |

|

|

|

| 15 | 16 |

|

|

| tDVWH | tWHDX |

DATA IN |

|

| DATA VALID |

|

|

|

| 20 |

|

|

|

| tWLQZ | 21 |

DATA OUT |

|

| HIGH IMPEDANCE | tWHQX |

| PREVIOUS DATA |

| ||

|

|

|

Figure 8. SRAM WRITE Cycle #2: E Controlled[7, 8]

|

| 11 |

|

|

| tAVAV |

|

ADDRESS |

|

|

|

18 |

| 14 | 19 |

tAVEL |

| tELEH | tEHAX |

E |

|

|

|

| 17 |

|

|

| tAVEH | 13 |

|

W |

| tWLEH |

|

|

|

| |

|

| 15 | 16 |

|

| tDVEH | tEHDX |

DATA IN |

|

| DATA VALID |

DATA OUT |

| HIGH IMPEDANCE |

|

|

|

|

Notes

7.If W is low when E goes low, the outputs remain in the

8.E or W must be ≥ VIH during address transitions.

Document #: | Page 7 of 23 |

[+] Feedback