STK17TA8

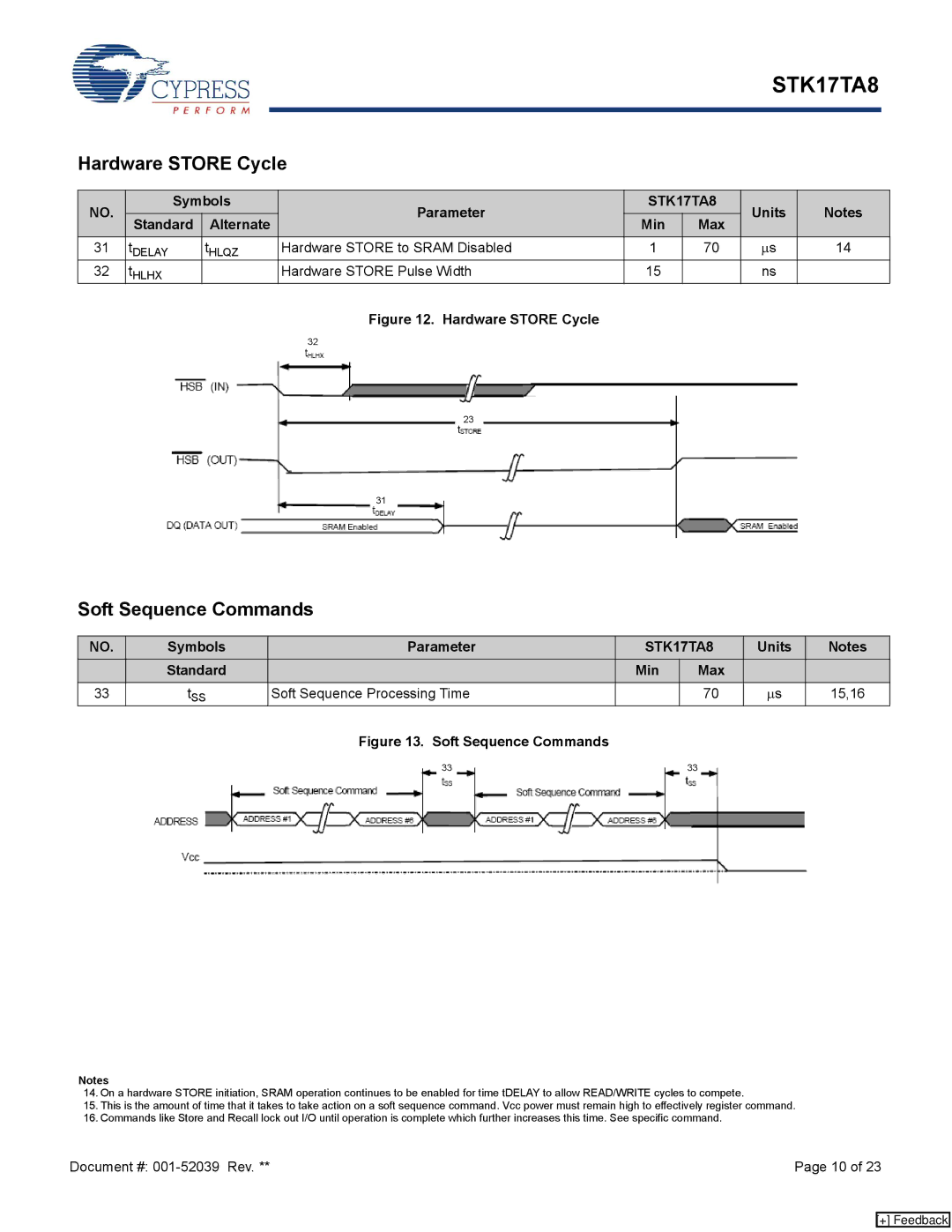

Hardware STORE Cycle

NO. | Symbols | Parameter | STK17TA8 | Units | Notes | |||

Standard | Alternate | Min | Max | |||||

|

|

|

| |||||

31 | tDELAY | tHLQZ | Hardware STORE to SRAM Disabled | 1 | 70 | μs | 14 | |

32 | tHLHX |

| Hardware STORE Pulse Width | 15 |

| ns |

| |

Figure 12. Hardware STORE Cycle

32

23

31

Soft Sequence Commands

NO. | Symbols | Parameter | STK17TA8 | Units | Notes | |

| Standard |

| Min | Max |

|

|

33 | tSS | Soft Sequence Processing Time |

| 70 | μs | 15,16 |

|

| Figure 13. Soft Sequence Commands |

|

|

|

|

|

| 33 |

| 33 |

|

|

Notes

14.On a hardware STORE initiation, SRAM operation continues to be enabled for time tDELAY to allow READ/WRITE cycles to compete.

15.This is the amount of time that it takes to take action on a soft sequence command. Vcc power must remain high to effectively register command.

16.Commands like Store and Recall lock out I/O until operation is complete which further increases this time. See specific command.

Document #: | Page 10 of 23 |

[+] Feedback