STK17TA8

128k X 8 AutoStore™ nvSRAM with Real Time Clock

Features

■nvSRAM Combined with Integrated Real Time Clock Functions (RTC, Watchdog Timer, Clock Alarm, Power Monitor)

■Capacitor or Battery Backup for RTC

■25, 45 ns Read Access and Read/Write Cycle Time

■Unlimited Read/Write Endurance

■Automatic nonvolatile STORE on Power Loss

■Nonvolatile STORE Under Hardware or Software Control

■Automatic RECALL to SRAM on Power Up

■Unlimited RECALL Cycles

■200K STORE Cycles

■

■Single 3 V +20%,

■Commercial and Industrial Temperatures

■

Description

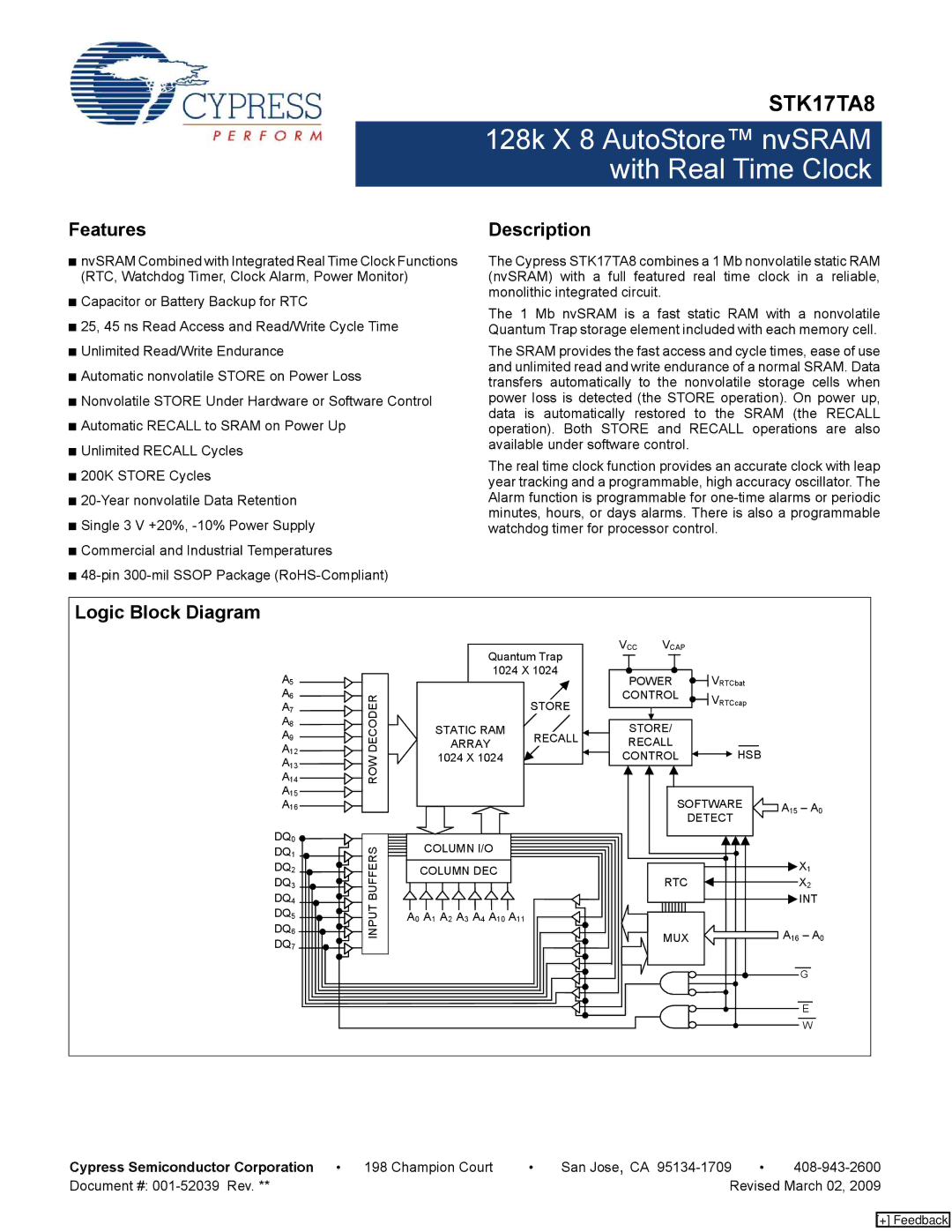

The Cypress STK17TA8 combines a 1 Mb nonvolatile static RAM (nvSRAM) with a full featured real time clock in a reliable, monolithic integrated circuit.

The 1 Mb nvSRAM is a fast static RAM with a nonvolatile Quantum Trap storage element included with each memory cell.

The SRAM provides the fast access and cycle times, ease of use and unlimited read and write endurance of a normal SRAM. Data transfers automatically to the nonvolatile storage cells when power loss is detected (the STORE operation). On power up, data is automatically restored to the SRAM (the RECALL operation). Both STORE and RECALL operations are also available under software control.

The real time clock function provides an accurate clock with leap year tracking and a programmable, high accuracy oscillator. The Alarm function is programmable for

Logic Block Diagram

|

| Quantum Trap | VCC | VCAP |

|

| |

|

|

|

|

|

| ||

A5 |

| 1024 X 1024 | POWER | VRTCbat |

| ||

|

|

|

| ||||

A6 | DECODER |

| STORE | CONTROL | VRTCcap |

| |

A7 |

|

|

|

| |||

|

|

|

|

| |||

A8 | STATIC RAM |

| STORE/ |

|

| ||

A9 | RECALL |

|

| ||||

ARRAY | RECALL |

|

| ||||

A12 |

| HSB |

| ||||

A13 | ROW | 1024 X 1024 |

| CONTROL |

| ||

A14 |

|

|

|

|

|

| |

A15 |

|

|

|

| SOFTWARE |

| |

A16 |

|

|

|

| A15 – A0 | ||

|

|

|

|

| DETECT |

| |

DQ0 | BUFFERS | COLUMN I/O |

|

|

|

|

|

DQ1 |

|

|

|

| X1 | ||

DQ2 | COLUMN DEC |

|

| RTC |

| ||

DQ3 |

|

|

|

| X2 | ||

DQ4 |

|

|

|

|

| INT | |

INPUT |

|

|

|

|

| ||

DQ5 | A0 A1 A2 A3 A4 A10 A11 |

|

|

|

|

| |

DQ6 |

|

|

| MUX |

| A16 – A0 | |

DQ7 |

|

|

|

| |||

|

|

|

|

|

|

| |

|

|

|

|

|

|

| G |

|

|

|

|

|

|

| E |

|

|

|

|

|

|

| W |

Cypress Semiconductor Corporation • 198 Champion Court | • | San Jose, CA | • | |

Document #: |

| Revised March 02, 2009 | ||

[+] Feedback