Dell™ PowerEdge™ M610 Technical Guidebook

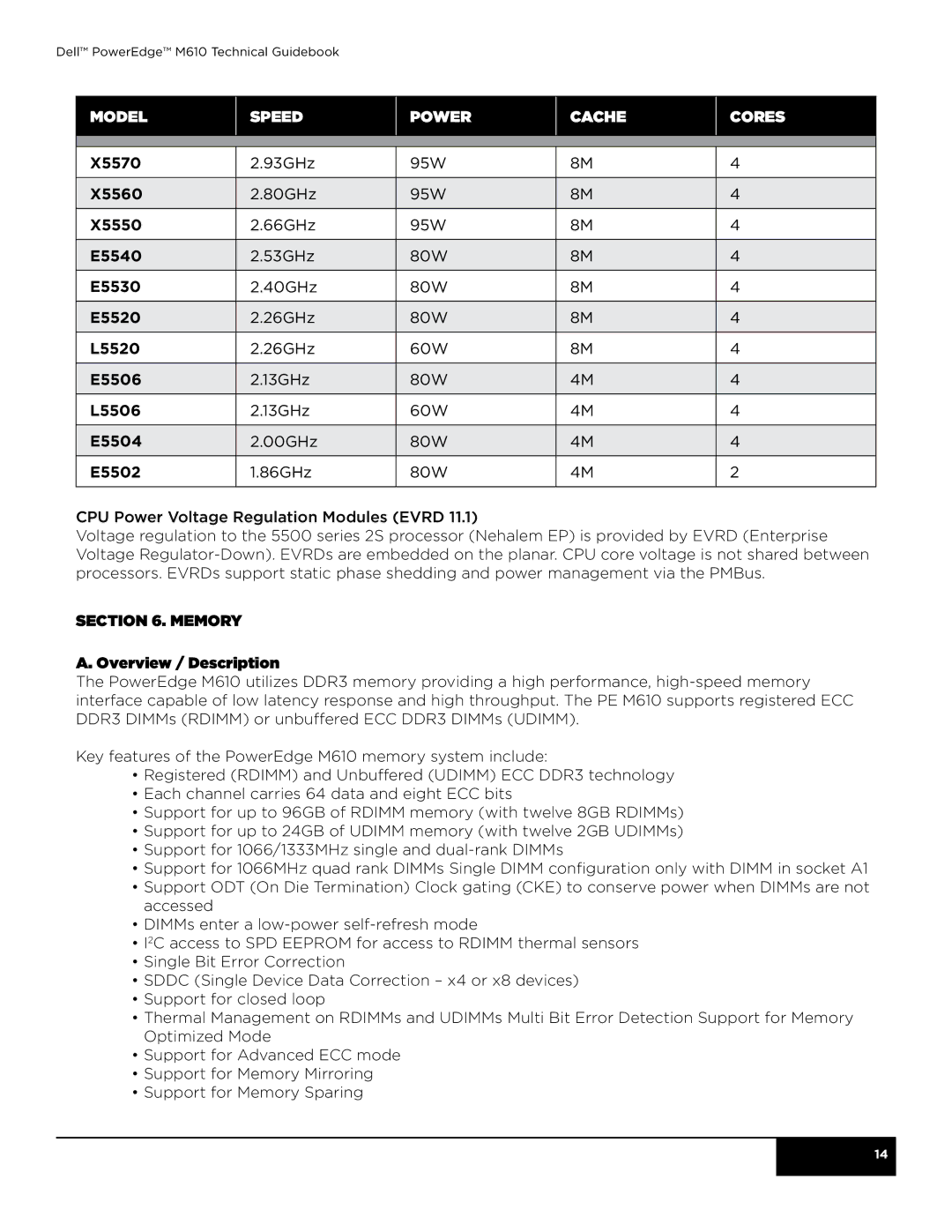

model

speed

power

cache

cores

|

|

|

|

|

X5570 | 2.93GHz | 95W | 8M | 4 |

|

|

|

|

|

X5560 | 2.80GHz | 95W | 8M | 4 |

|

|

|

|

|

X5550 | 2.66GHz | 95W | 8M | 4 |

|

|

|

|

|

E5540 | 2.53GHz | 80W | 8M | 4 |

|

|

|

|

|

E5530 | 2.40GHz | 80W | 8M | 4 |

|

|

|

|

|

E5520 | 2.26GHz | 80W | 8M | 4 |

|

|

|

|

|

L5520 | 2.26GHz | 60W | 8M | 4 |

|

|

|

|

|

E5506 | 2.13GHz | 80W | 4M | 4 |

|

|

|

|

|

L5506 | 2.13GHz | 60W | 4M | 4 |

|

|

|

|

|

E5504 | 2.00GHz | 80W | 4M | 4 |

|

|

|

|

|

E5502 | 1.86GHz | 80W | 4M | 2 |

|

|

|

|

|

CPU Power Voltage Regulation Modules (EVRD 11.1)

Voltage regulation to the 5500 series 2S processor (Nehalem EP) is provided by EVRD (Enterprise Voltage

Section 6. Memory

A. Overview / Description

The PowerEdge M610 utilizes DDR3 memory providing a high performance,

Key features of the PowerEdge M610 memory system include:

•Registered (RDIMM) and Unbuffered (UDIMM) ECC DDR3 technology

•Each channel carries 64 data and eight ECC bits

•Support for up to 96GB of RDIMM memory (with twelve 8GB RDIMMs)

•Support for up to 24GB of UDIMM memory (with twelve 2GB UDIMMs)

•Support for 1066/1333MHz single and

•Support for 1066MHz quad rank DIMMs Single DIMM configuration only with DIMM in socket A1

•Support ODT (On Die Termination) Clock gating (CKE) to conserve power when DIMMs are not accessed

•DIMMs enter a

•I2C access to SPD EEPROM for access to RDIMM thermal sensors

•Single Bit Error Correction

•SDDC (Single Device Data Correction – x4 or x8 devices)

•Support for closed loop

•Thermal Management on RDIMMs and UDIMMs Multi Bit Error Detection Support for Memory

Optimized Mode

•Support for Advanced ECC mode

•Support for Memory Mirroring

•Support for Memory Sparing

14