Dell™ PowerEdge™ M610 Technical Guidebook

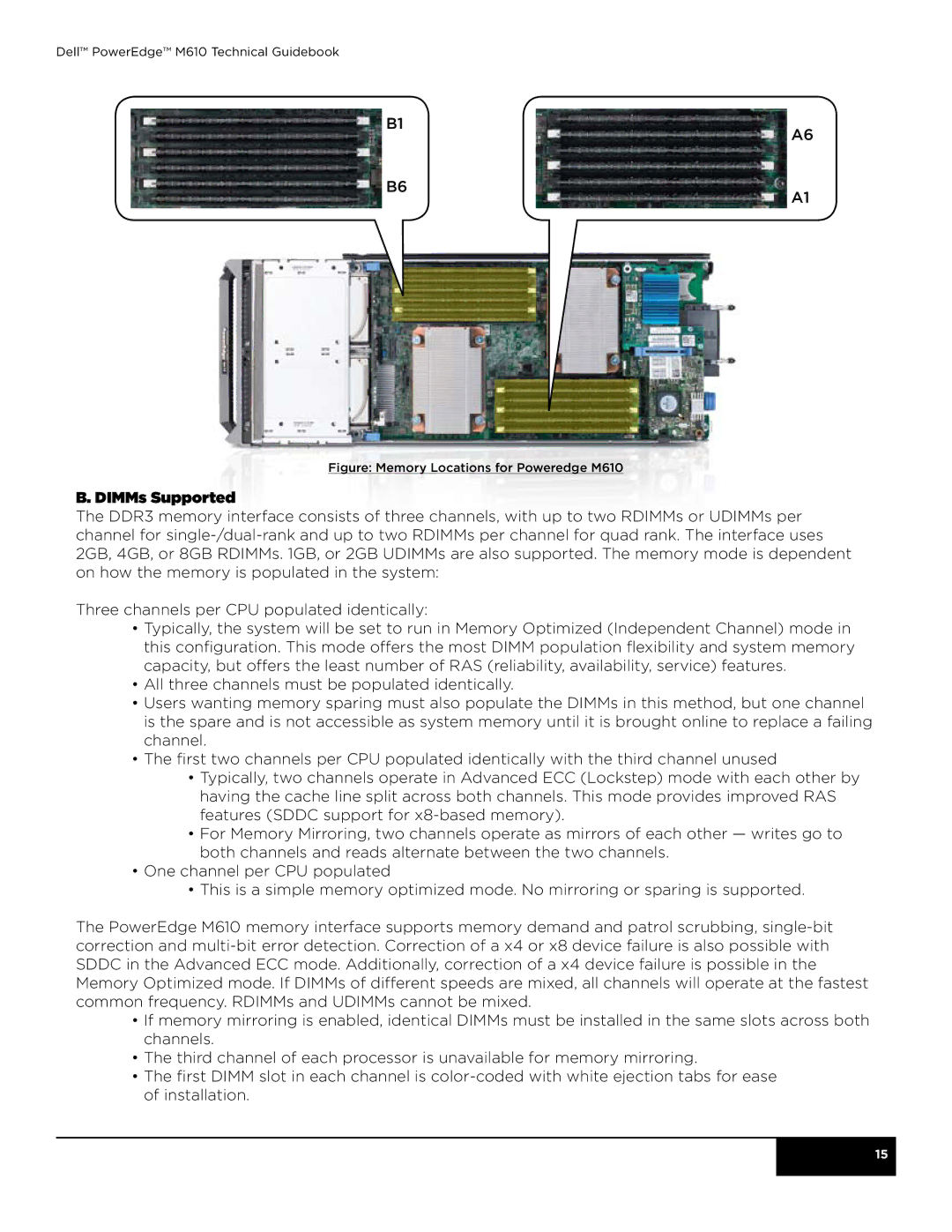

B1 | A6 |

| |

B6 | A1 |

|

Figure: Memory Locations for Poweredge M610

B. DIMMs Supported

The DDR3 memory interface consists of three channels, with up to two RDIMMs or UDIMMs per channel for

Three channels per CPU populated identically:

•Typically, the system will be set to run in Memory Optimized (Independent Channel) mode in this configuration. This mode offers the most DIMM population flexibility and system memory capacity, but offers the least number of RAS (reliability, availability, service) features.

•All three channels must be populated identically.

•Users wanting memory sparing must also populate the DIMMs in this method, but one channel is the spare and is not accessible as system memory until it is brought online to replace a failing channel.

•The first two channels per CPU populated identically with the third channel unused

•Typically, two channels operate in Advanced ECC (Lockstep) mode with each other by having the cache line split across both channels. This mode provides improved RAS features (SDDC support for

•For Memory Mirroring, two channels operate as mirrors of each other — writes go to both channels and reads alternate between the two channels.

•One channel per CPU populated

•This is a simple memory optimized mode. No mirroring or sparing is supported.

The PowerEdge M610 memory interface supports memory demand and patrol scrubbing,

•If memory mirroring is enabled, identical DIMMs must be installed in the same slots across both channels.

•The third channel of each processor is unavailable for memory mirroring.

•The first DIMM slot in each channel is

15