Dell™ PowerEdge™ M610 Technical Guidebook

Section 7. Chipset

A. Overview / Description

The PowerEdge M610 planar incorporated the Intel 5520 chipset (code named Tylersburg) for I/O and processor interfacing. Tylersburg is designed to support Intel's 5500 series processors (code named

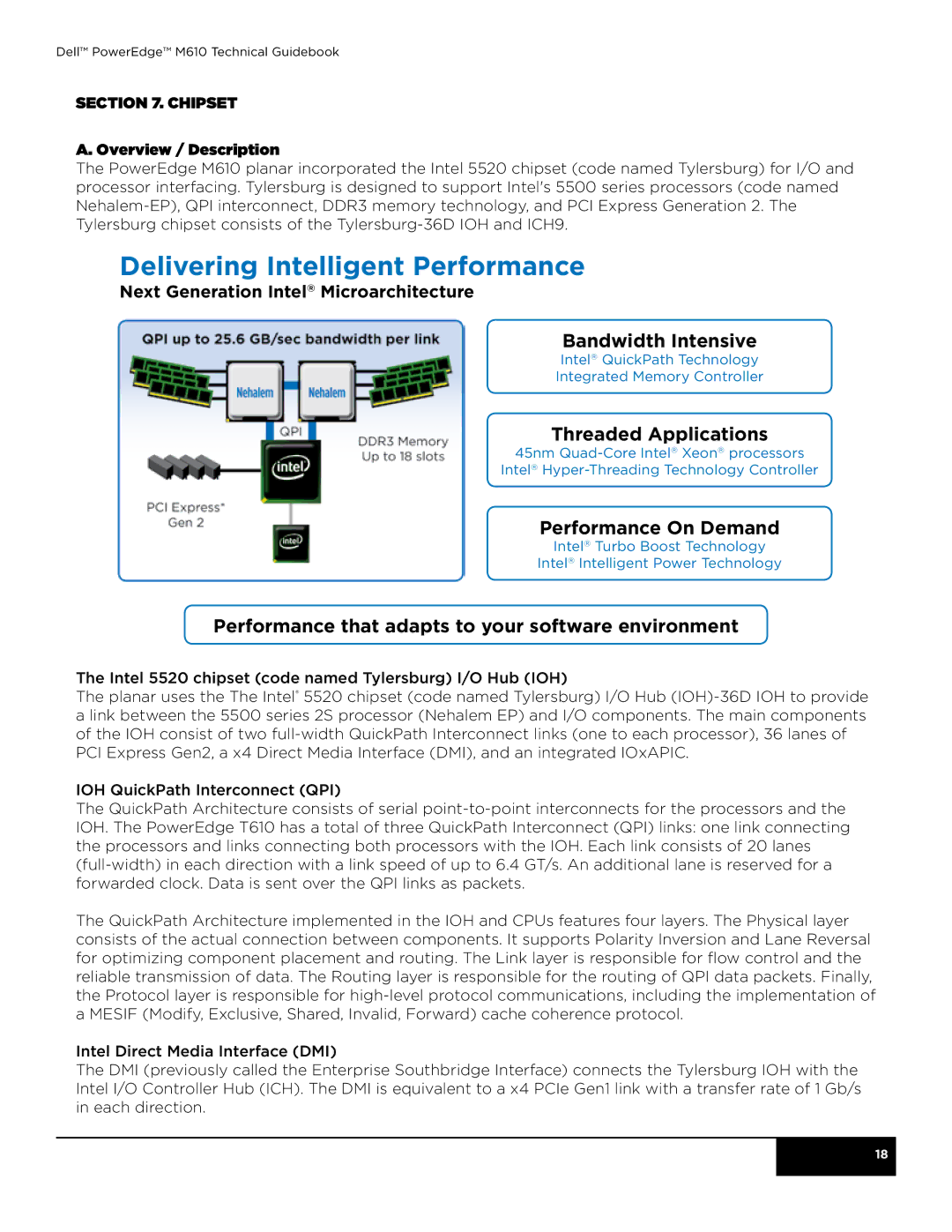

Delivering Intelligent Performance

Next Generation Intel® Microarchitecture

Bandwidth Intensive

Intel® QuickPath Technology

Integrated Memory Controller

Threaded Applications

45nm

Performance On Demand

Intel® Turbo Boost Technology

Intel® Intelligent Power Technology

Performance that adapts to your software environment

The Intel 5520 chipset (code named Tylersburg) I/O Hub (IOH)

The planar uses the The Intel® 5520 chipset (code named Tylersburg) I/O Hub

IOH QuickPath Interconnect (QPI)

The QuickPath Architecture consists of serial

The QuickPath Architecture implemented in the IOH and CPUs features four layers. The Physical layer consists of the actual connection between components. It supports Polarity Inversion and Lane Reversal for optimizing component placement and routing. The Link layer is responsible for flow control and the reliable transmission of data. The Routing layer is responsible for the routing of QPI data packets. Finally, the Protocol layer is responsible for

Intel Direct Media Interface (DMI)

The DMI (previously called the Enterprise Southbridge Interface) connects the Tylersburg IOH with the Intel I/O Controller Hub (ICH). The DMI is equivalent to a x4 PCIe Gen1 link with a transfer rate of 1 Gb/s in each direction.

18