MB15F74UV

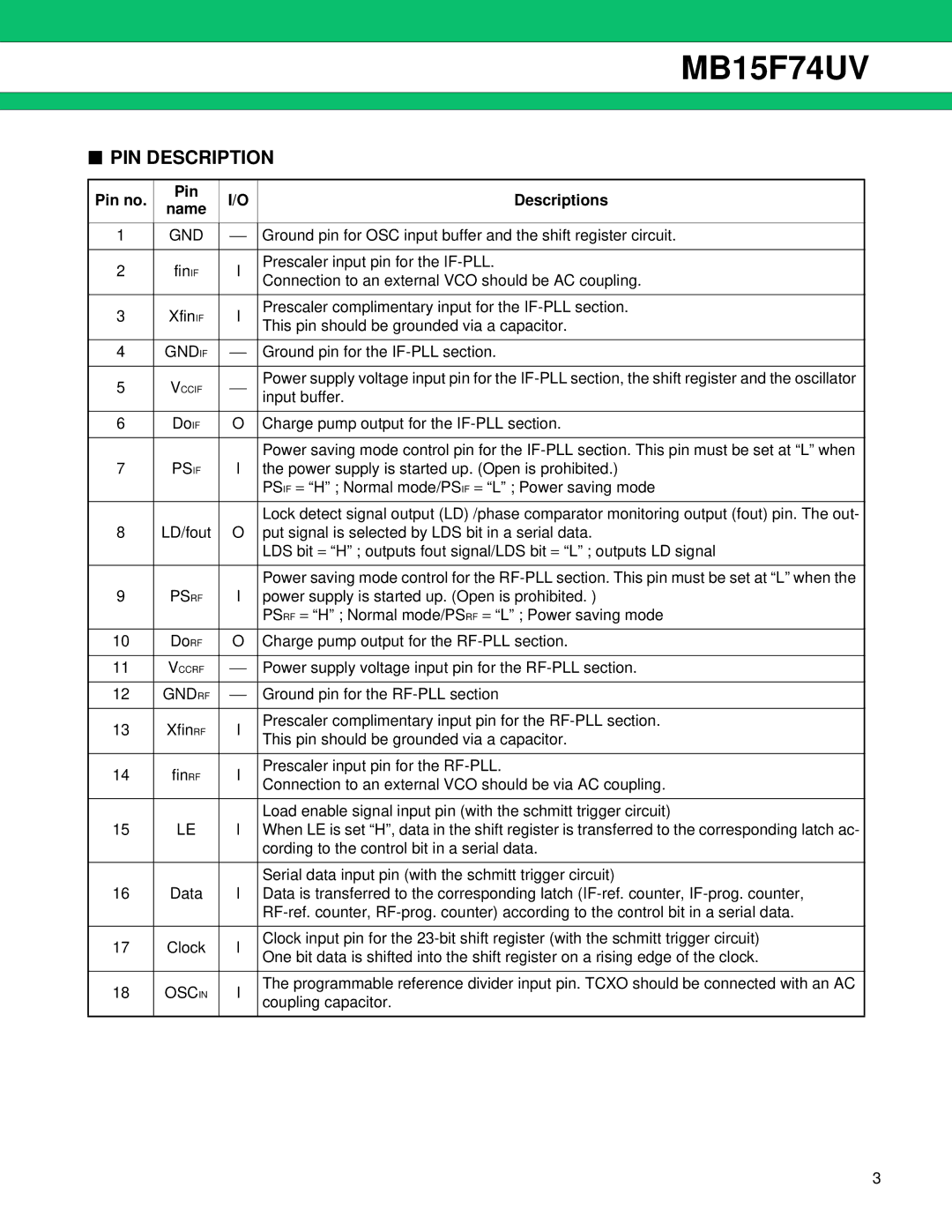

■PIN DESCRIPTION

Pin no. | Pin | I/O | Descriptions | |

name | ||||

|

|

| ||

|

|

|

| |

1 | GND | | Ground pin for OSC input buffer and the shift register circuit. | |

|

|

|

| |

2 | finIF | I | Prescaler input pin for the | |

Connection to an external VCO should be AC coupling. | ||||

|

|

| ||

|

|

|

| |

3 | XfinIF | I | Prescaler complimentary input for the | |

This pin should be grounded via a capacitor. | ||||

|

|

| ||

|

|

|

| |

4 | GNDIF | | Ground pin for the | |

|

|

|

| |

5 | VCCIF | | Power supply voltage input pin for the | |

input buffer. | ||||

|

|

| ||

|

|

|

| |

6 | DoIF | O | Charge pump output for the | |

|

|

|

| |

|

|

| Power saving mode control pin for the | |

7 | PSIF | I | the power supply is started up. (Open is prohibited.) | |

|

|

| PSIF = “H” ; Normal mode/PS IF = “L” ; Power saving mode | |

|

|

|

| |

|

|

| Lock detect signal output (LD) /phase comparator monitoring output (fout) pin. The out- | |

8 | LD/fout | O | put signal is selected by LDS bit in a serial data. | |

|

|

| LDS bit = “H” ; outputs fout signal/LDS bit = “L” ; outputs LD signal | |

|

|

|

| |

|

|

| Power saving mode control for the | |

9 | PSRF | I | power supply is started up. (Open is prohibited. ) | |

|

|

| PSRF = “H” ; Normal mode/PS RF = “L” ; Power saving mode | |

|

|

|

| |

10 | DoRF | O | Charge pump output for the | |

|

|

|

| |

11 | VCCRF | | Power supply voltage input pin for the | |

|

|

|

| |

12 | GNDRF | | Ground pin for the | |

|

|

|

| |

13 | XfinRF | I | Prescaler complimentary input pin for the | |

This pin should be grounded via a capacitor. | ||||

|

|

| ||

|

|

|

| |

14 | finRF | I | Prescaler input pin for the | |

Connection to an external VCO should be via AC coupling. | ||||

|

|

| ||

|

|

|

| |

|

|

| Load enable signal input pin (with the schmitt trigger circuit) | |

15 | LE | I | When LE is set “H”, data in the shift register is transferred to the corresponding latch ac- | |

|

|

| cording to the control bit in a serial data. | |

|

|

|

| |

|

|

| Serial data input pin (with the schmitt trigger circuit) | |

16 | Data | I | Data is transferred to the corresponding latch | |

|

|

| ||

|

|

|

| |

17 | Clock | I | Clock input pin for the | |

One bit data is shifted into the shift register on a rising edge of the clock. | ||||

|

|

| ||

|

|

|

| |

18 | OSCIN | I | The programmable reference divider input pin. TCXO should be connected with an AC | |

coupling capacitor. | ||||

|

|

| ||

|

|

|

|

3