GMS90X5XC Series | HYUNDAI MicroElectronics |

Power Saving Modes

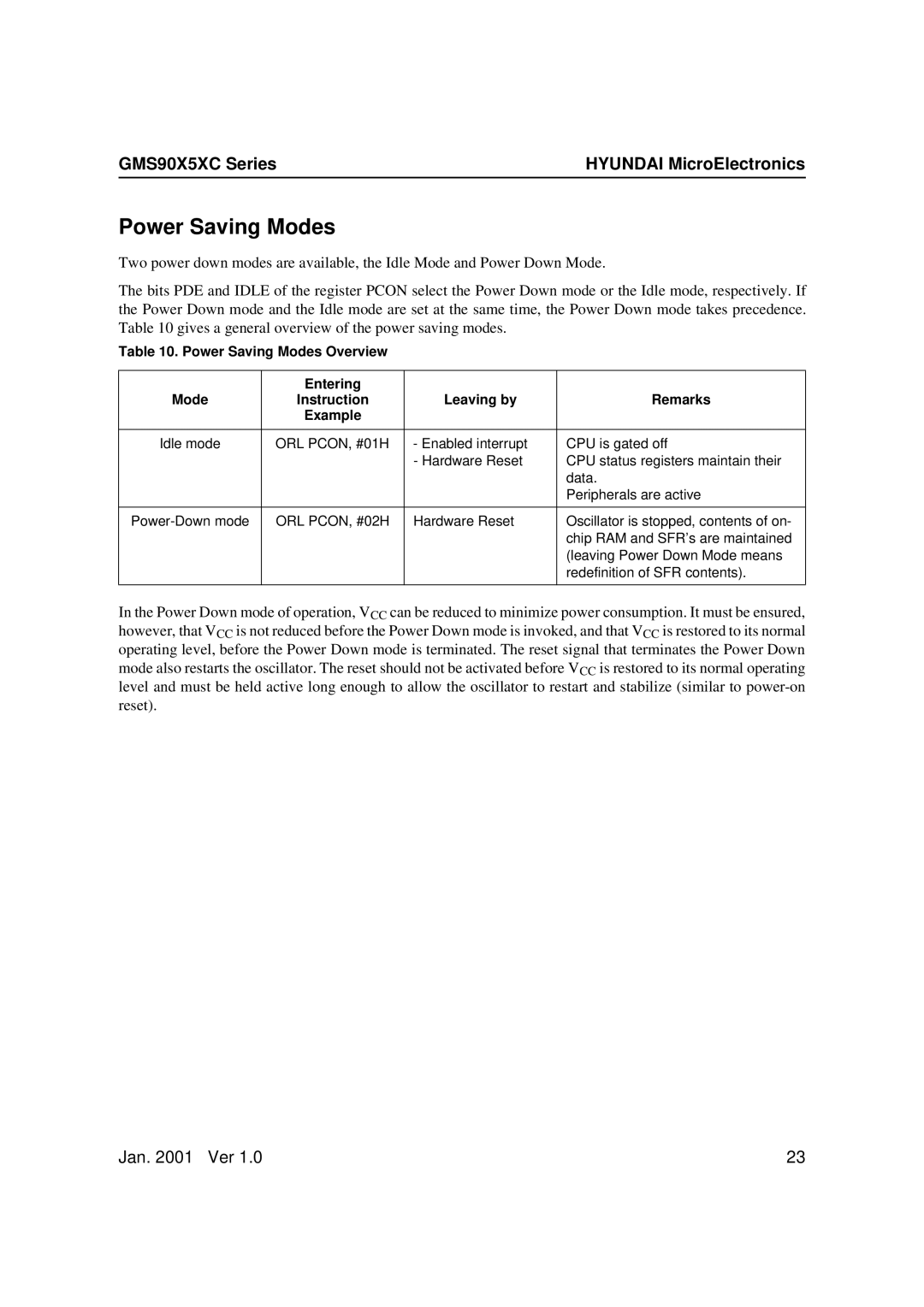

Two power down modes are available, the Idle Mode and Power Down Mode.

The bits PDE and IDLE of the register PCON select the Power Down mode or the Idle mode, respectively. If the Power Down mode and the Idle mode are set at the same time, the Power Down mode takes precedence. Table 10 gives a general overview of the power saving modes.

Table 10. Power Saving Modes Overview

| Entering |

|

|

Mode | Instruction | Leaving by | Remarks |

| Example |

|

|

|

|

|

|

Idle mode | ORL PCON, #01H | - Enabled interrupt | CPU is gated off |

|

| - Hardware Reset | CPU status registers maintain their |

|

|

| data. |

|

|

| Peripherals are active |

|

|

|

|

ORL PCON, #02H | Hardware Reset | Oscillator is stopped, contents of on- | |

|

|

| chip RAM and SFR’s are maintained |

|

|

| (leaving Power Down Mode means |

|

|

| redefinition of SFR contents). |

|

|

|

|

In the Power Down mode of operation, VCC can be reduced to minimize power consumption. It must be ensured, however, that VCC is not reduced before the Power Down mode is invoked, and that VCC is restored to its normal operating level, before the Power Down mode is terminated. The reset signal that terminates the Power Down mode also restarts the oscillator. The reset should not be activated before VCC is restored to its normal operating level and must be held active long enough to allow the oscillator to restart and stabilize (similar to

Jan. 2001 Ver 1.0 | 23 |