HYUNDAI MicroElectronics | GMS90X5XC Series |

CPU

The GMS90X5XC series is efficient both as a controller and as an arithmetic processor. It has extensive facili- ties for binary and BCD arithmetic and excels in its

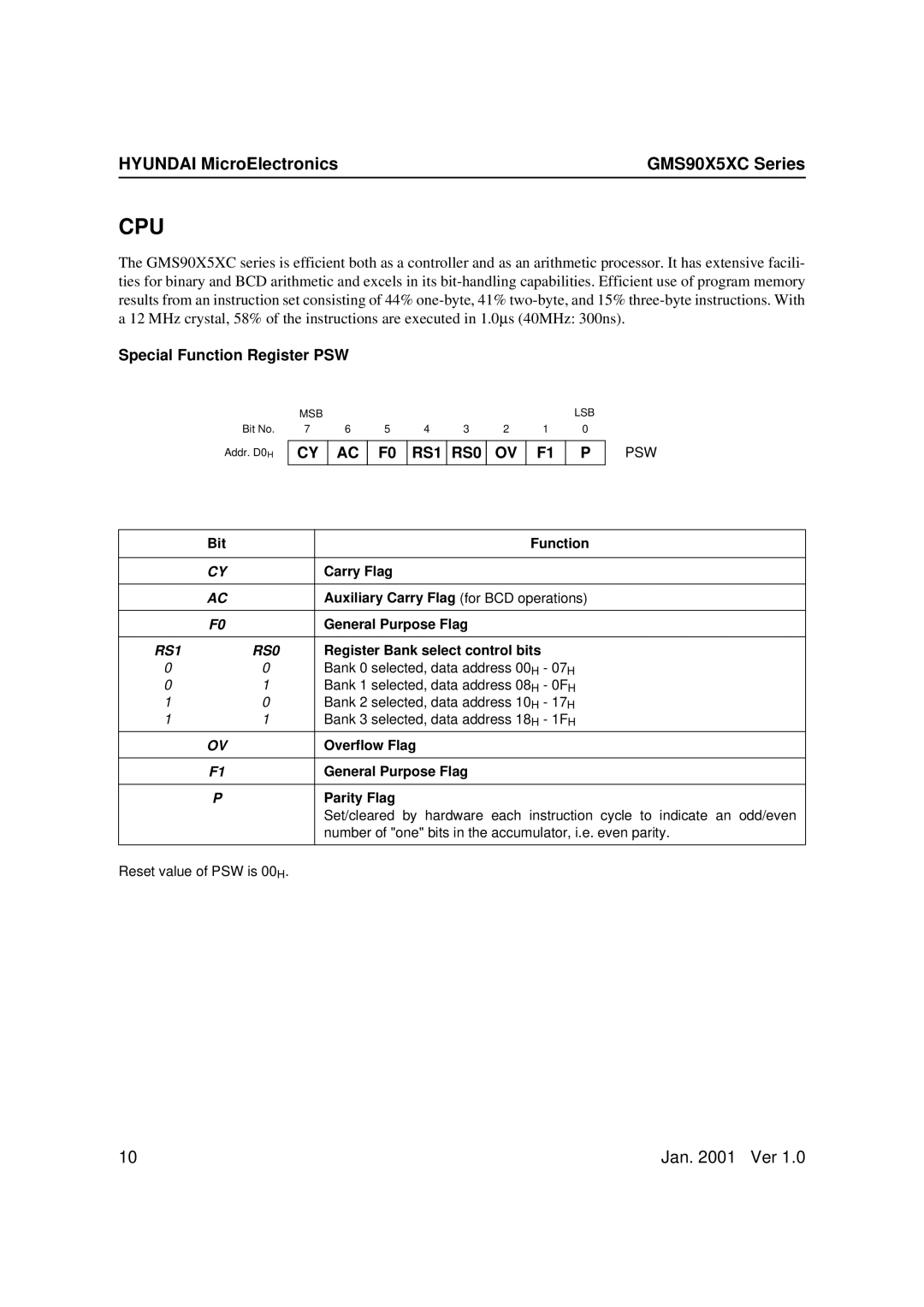

Special Function Register PSW

Bit No.

Addr. D0H

MSB |

|

|

|

|

|

| LSB |

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|

|

|

|

|

|

|

|

CY | AC | F0 | RS1 | RS0 | OV | F1 | P |

|

|

|

|

|

|

|

|

PSW

Bit |

| Function |

|

|

|

CY |

| Carry Flag |

|

|

|

AC |

| Auxiliary Carry Flag (for BCD operations) |

|

|

|

F0 |

| General Purpose Flag |

|

|

|

RS1 | RS0 | Register Bank select control bits |

0 | 0 | Bank 0 selected, data address 00H - 07H |

0 | 1 | Bank 1 selected, data address 08H - 0FH |

1 | 0 | Bank 2 selected, data address 10H - 17H |

1 | 1 | Bank 3 selected, data address 18H - 1FH |

OV |

| Overflow Flag |

|

|

|

F1 |

| General Purpose Flag |

|

|

|

P |

| Parity Flag |

|

| Set/cleared by hardware each instruction cycle to indicate an odd/even |

|

| number of "one" bits in the accumulator, i.e. even parity. |

|

|

|

Reset value of PSW is 00H.

10 | Jan. 2001 Ver 1.0 |