536EX Chipset

Developer’s Manual

January

536EX Chipset Developer’s Manual

Intel Confidential

Contents

Contents

Figures

Tables

Description

Revision History

Date

Revision

1.1Controllerless Modem Driver Overview

Introduction

Kernel - ring0

Figure 1. WDM Driver Block Diagram

1.1.2Windows 95 and Windows

User applications

1.2V.90/V.92 and V.34 Data Modes

Figure 2. VxD Mini Port Driver Block Diagram

1.3Modem Connection Overview

Table 1. DTE-to-DCEData Rates for Each Mode

Table 2. DCE-to-DCEData Rates for Each Mode

Table 3. DCE-to-ISPData Rates for V.90 Mode

Table 4. DTE-ModemData Rate Response Codes

1.4.1Sending Commands

1.4.3Dial Modifier

1.4.2AT Escape Sequences

AT Command Summary Tables

AT Command Summary Tables

Table 5. Data Mode Command Summary

Table 5. Data Mode Command Summary Continued

Result code type

536EX Chipset Developer’s Manual

Generate data mode calling tone

Table 6. V.44/V.42/V.42 bis MNP Command Summary

536EX Chipset Developer’s Manual

Table 8. Fax Class 1 Command Summary

Table 7. Fax Identity Command Summary

Table 10. Voice DTE→DCE Character Pairs

Table 9. IS-101Voice Command Summary

Table 11. Voice DTE←DCE Character Pairs

Table 10. Voice DTE→DCE Character Pairs Continued

Table 11. Voice DTE←DCE Character Pairs Continued

Table 12. Dial Modifiers

Table 13. S-RegisterSummary

Table 13. S-RegisterSummary Continued

Data Mode AT COMMANDS

Data Mode AT COMMANDS

•ATW2

Table 14. Data Reporting Wn Mapping

Figure 3. Example of a Remote Connection

ATW0

Data Mode AT COMMANDS

+FMFR?, +FMDL?, +FREV?

3.6Online Command Mode Escape Codes, On

3.7Hanging Up Hn, S10, Zn, &D2

3.8Modem-to-ModemConnection Data Rates

Data Mode AT COMMANDS

+++AT

+PMH=0

+PCW=0

+VCID=1

Data Mode AT COMMANDS

hook to connect the call. Now you can answer the phone and talk. After completing your voice conversation, the modem will issue another +PMHF and ATO command to initiate a Quick Connect. If the server rejects the request to go on hold, the user can stay on line ATO command issued or disconnect from his initial data connection ATH command issued

Table 16. Supported Modulation Types

3.9.1Local Analog Loopback AT&T1

3.9Diagnostic Testing S18, &Tn

Local Modem or Test Modem

3.9.2Local Analog Loopback With Self-TestAT&T8

LOCAL MODEM

Figure 6. Local Analog Loopback Test

Licensing Requirements for Hayes Escape Sequence

3.10.1Time-IndependentEscape Sequence

<char1><char2><char3><AT command><contents of S3>

Format

char1 = char2 = char3 = escape character S2

3.10.2Hayes* Escape Sequence

Table 18. Data Mode Command Descriptions

Data Mode AT COMMANDS

Sn=x

Data Mode AT COMMANDS

Intel Confidential

536EX Chipset Developer’s Manual

536EX Chipset Developer’s Manual

AT&V0

Data Mode AT COMMANDS

Command Default

Indication

Definition

1, 0,

Data Mode AT COMMANDS

+ESR

+ETBM

1, 1,

+ILRR=m

+GMR

+GSN

+IFC

536EX Chipset Developer’s Manual

see ‘m’

<carrier>

Description

+MS=m

+PMHR

+PHSW=

+PMHF

<value>

Data Mode AT COMMANDS

Error Correction and Data Compression4

Error Correction and Data Compression

Table 19. Operating Modes

NOTES

Table 20. Resulting +ES Connection Types

Error Correction and Data Compression

Intel Confidential

536EX Chipset Developer’s Manual

Error Correction and Data Compression

<max string>

+DR=m

direction

+DS=m

+EFCS=m

3768

+ER=m

+ES=m

Fax Class 1 AT Commands

Fax Class 1 AT Commands

5.1Fax Identity Commands

5.2Fax Class 1 Commands

Table 23. <mod> Selection Table

Figure 8. T.30 HDLC Frame Format

Table 24. Fax Mode Command Descriptions

shown in Table 23 on page

Table 24. Fax Mode Command Descriptions Continued

+FRH=m

Refer to Table 23 on page

+FTH=m

IS-101Voice Mode AT Commands

IS-101Voice Mode AT Commands

Table 25. Voice Mode Command Descriptions

6.1DTMF Detection Reporting

6.2Relay Control

m = <deassert>, <assert>

+FLO=m

+VDR=m

m=<enable>, <report>

+VEM=m

m = <mask>

Intel Confidential

+VIP

+VLS=m

Preassigned Voice I/O Labels

Relay/Playback Control: cont

Voice I/O Primitive Codes

+VRX

m = <sds>, <sdi>

+VSD=m

m= <cml>, <vsr>, <scs>, <sel>

+VSM=m

Transmission: Range:

+VSP=m

Compression Method Selection: cont

factory default is ‘0’

none

+VTS=m

DTMF and Tone Generation: cont

Command

Default

Description

S-Registers

Table 26. S-RegisterCommand Descriptions

S-Registers

Intel Confidential

S-Registers

536EX Chipset Developer’s Manual

Intel Confidential

S-Registers

536EX Chipset Developer’s Manual

Intel Confidential

S-Registers

536EX Chipset Developer’s Manual

Intel Confidential

Caller ID

Caller ID

Table 27. Caller ID Tags for Formatted Reporting

NMBR =

RING DATE = TIME = NMBR = NAME = DOE JOHN MESG =

RING RING

<DLE> R

Figure 11. UART Emulation in Intelsdb.VxD

Parallel Host Interface 16C450/16C550A

UART

Parallel Host Interface 16C450/16C550A UART

UART Receiver Flow Diagram

UART Transmitter Flow Diagram

NAME

REGISTER

BIT NUMBER

ADDRESS

Figure 15. Modem Status Register MSR

9.2.1Scratch Register SCR

9.2.2Modem Status Register MSR

Figure 14. Scratch Register SCR

Figure 16. Line Status Register LSR

9.2.3Line Status Register LSR

Figure 18. Line Control Register LCR

9.2.4Modem Control Register MCR

9.2.5Line Control Register LCR

Figure 17. Modem Control Register MCR

9.2.6FIFO Control Register FCR

Register

Figure 19. FIFO Control Register FCR

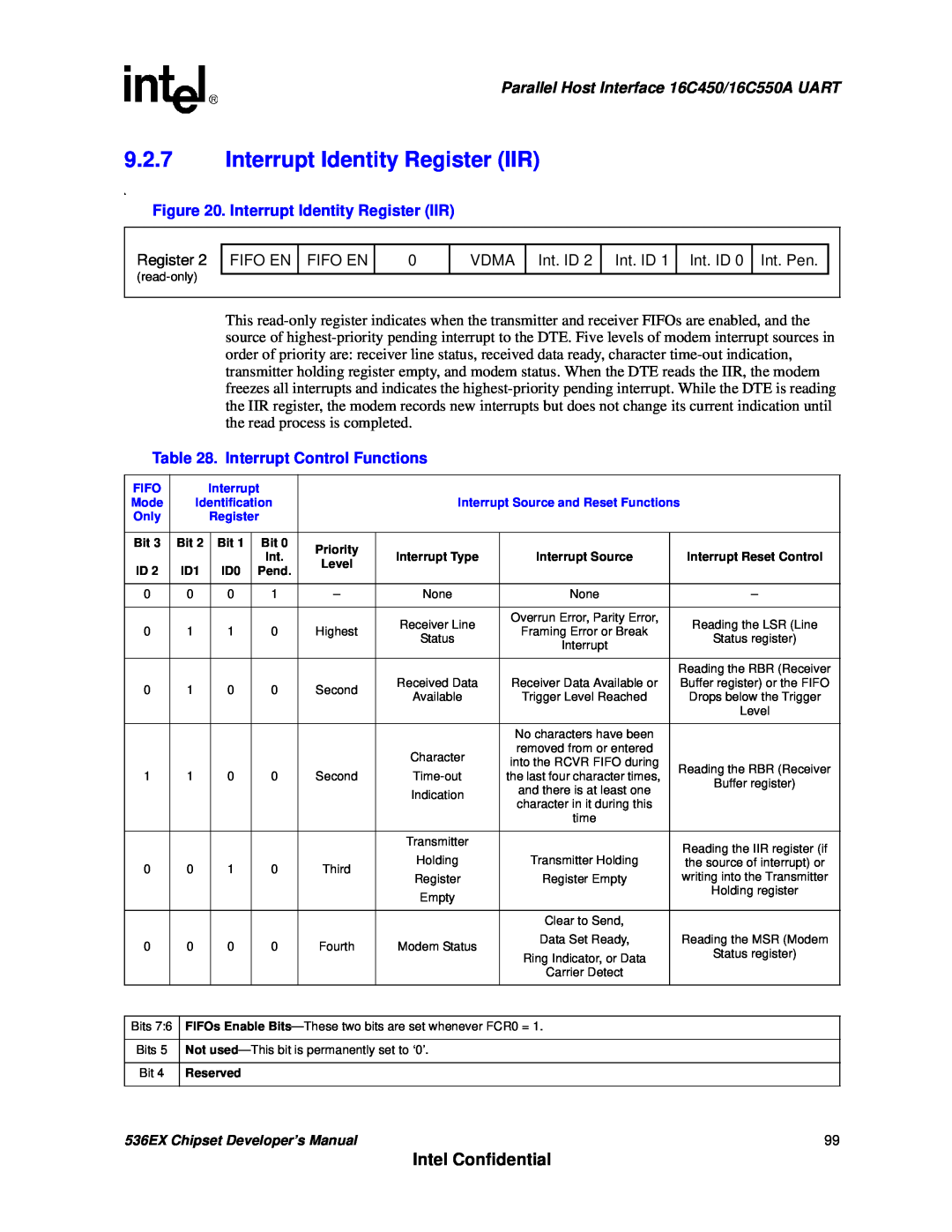

9.2.7Interrupt Identity Register IIR

Figure 20. Interrupt Identity Register IIR

Table 28. Interrupt Control Functions

Figure 22. Transmitter Holding Register THR

9.2.8Interrupt Enable Register IER

Figure 21. Interrupt Enable Register IER

9.2.9Transmitter Holding Register THR

Figure 24. Divisor Latch Registers DLM and DLL

9.2.10Receiver Buffer Register RBR

9.2.11Divisor Latch Registers DLM and DLL

Figure 23. Receiver Buffer Register RBR

9.316C550A UART FIFO Operation

9.3.1FIFO Interrupt Mode Operation

9.3.2FIFO Polled Mode Operation

Intel Confidential

Parallel Host Interface 16C450/16C550A UART

536EX Chipset Developer’s Manual