|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| DS5001FP |

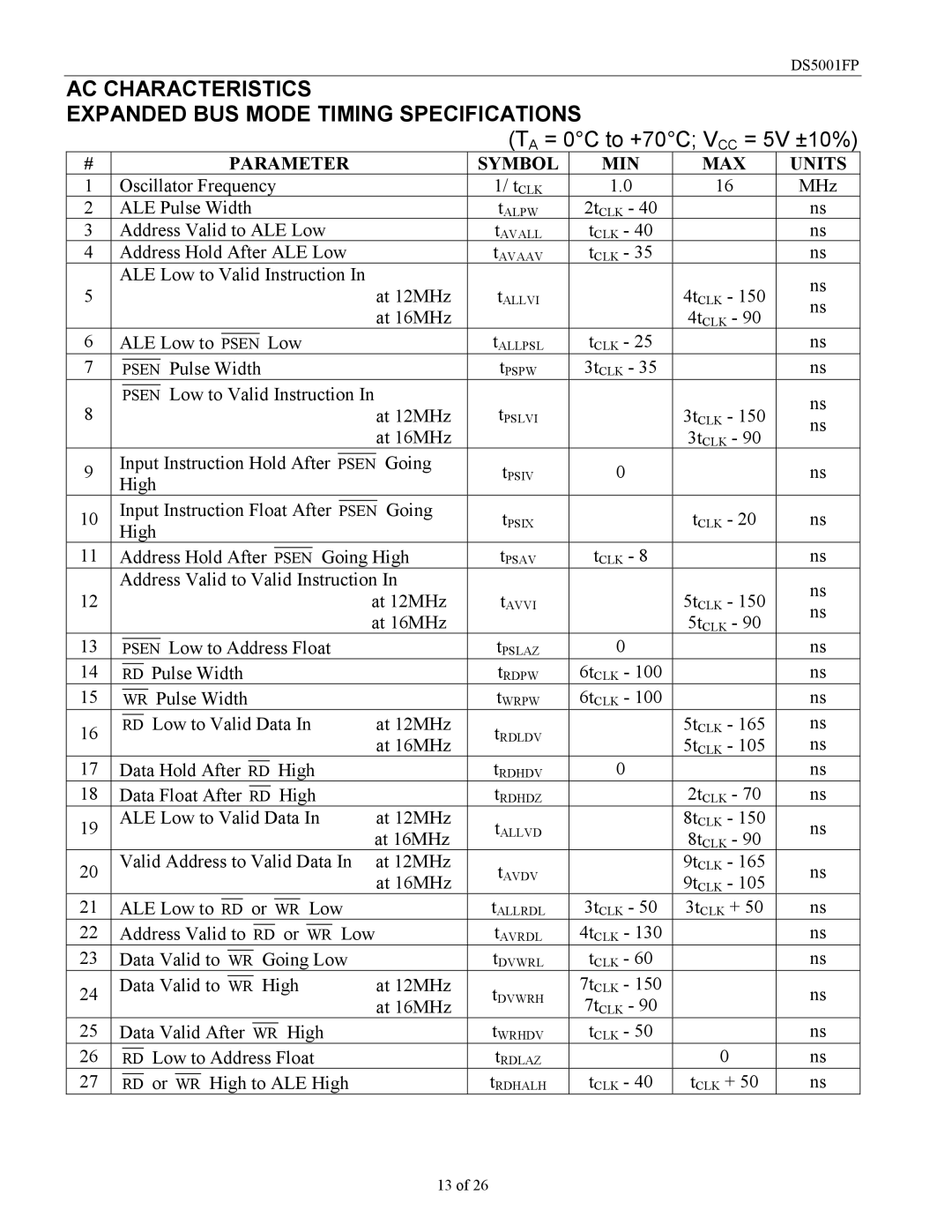

| AC CHARACTERISTICS |

|

|

|

|

|

|

| |||||||||||||||||||||||||||||

| EXPANDED BUS MODE TIMING SPECIFICATIONS |

|

| ||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| (TA = 0°C to +70°C; VCC = 5V ±10%) | |||

| # |

|

|

|

|

|

|

|

|

|

|

| PARAMETER |

|

|

| SYMBOL | MIN | MAX | UNITS | |||||||||||||||||

| 1 | Oscillator Frequency |

|

|

| 1/ tCLK | 1.0 | 16 | MHz | ||||||||||||||||||||||||||||

| 2 | ALE Pulse Width |

|

|

| tALPW | 2tCLK - 40 |

| ns | ||||||||||||||||||||||||||||

| 3 | Address Valid to ALE Low |

|

|

| tAVALL | tCLK - 40 |

| ns | ||||||||||||||||||||||||||||

| 4 | Address Hold After ALE Low |

|

|

| tAVAAV | tCLK - 35 |

| ns | ||||||||||||||||||||||||||||

| 5 | ALE Low to Valid Instruction In |

| at 12MHz | tALLVI |

| 4tCLK - 150 | ns | |||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ns | |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| at 16MHz |

|

| 4tCLK - 90 | ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

| 6 | ALE Low to |

|

|

|

|

|

|

|

| Low |

|

|

| tALLPSL | tCLK - 25 |

| ns | |||||||||||||||||||

PSEN |

|

|

|

| |||||||||||||||||||||||||||||||||

| 7 |

|

|

|

|

|

|

| Pulse Width |

|

|

| tPSPW | 3tCLK - 35 |

| ns | |||||||||||||||||||||

PSEN |

|

|

|

| |||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

| Low to Valid Instruction In |

|

|

|

| ||||||||||||||||||||||||

| 8 |

| PSEN | tPSLVI |

|

| ns | ||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| at 12MHz |

| 3tCLK - 150 | ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ns | |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| at 16MHz |

|

| 3tCLK - 90 | ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

| Input Instruction Hold After |

|

|

|

| Going |

|

|

|

| ||||||||||||||||||||||||||

| 9 | PSEN | tPSIV | 0 |

| ns | |||||||||||||||||||||||||||||||

| High |

|

|

|

| ||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||||||||

|

| Input Instruction Float After |

|

|

| Going |

|

|

|

| |||||||||||||||||||||||||||

| 10 | PSEN | tPSIX |

| tCLK - 20 | ns | |||||||||||||||||||||||||||||||

| High |

|

|

|

| ||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||||||||

| 11 | Address Hold After |

|

|

|

| Going High | tPSAV | tCLK - 8 |

| ns | ||||||||||||||||||||||||||

PSEN |

| ||||||||||||||||||||||||||||||||||||

|

| Address Valid to Valid Instruction In |

|

|

| ns | |||||||||||||||||||||||||||||||

| 12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| at 12MHz | tAVVI |

| 5tCLK - 150 | |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ns | ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| at 16MHz |

|

| 5tCLK - 90 | |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

| 13 |

|

|

|

|

|

| Low to Address Float |

|

|

| tPSLAZ | 0 |

| ns | ||||||||||||||||||||||

| PSEN |

|

|

|

| ||||||||||||||||||||||||||||||||

| 14 |

|

|

|

|

| Pulse Width |

|

|

| tRDPW | 6tCLK - 100 |

| ns | |||||||||||||||||||||||

| RD |

|

|

|

| ||||||||||||||||||||||||||||||||

| 15 |

|

|

|

|

| Pulse Width |

|

|

| tWRPW | 6tCLK - 100 |

| ns | |||||||||||||||||||||||

|

| WR |

|

|

|

| |||||||||||||||||||||||||||||||

|

|

|

|

|

| Low to Valid Data In |

| at 12MHz |

|

| 5tCLK - 165 | ns | |||||||||||||||||||||||||

| 16 |

| RD |

| tRDLDV |

| |||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| at 16MHz |

| 5tCLK - 105 | ns | |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

| 17 | Data Hold After |

|

|

|

|

|

|

|

| High |

|

|

| tRDHDV | 0 |

| ns | |||||||||||||||||||

RD |

|

|

|

| |||||||||||||||||||||||||||||||||

| 18 | Data Float After |

|

|

|

|

|

|

| High |

|

|

| tRDHDZ |

| 2tCLK - 70 | ns | ||||||||||||||||||||

RD |

|

|

|

| |||||||||||||||||||||||||||||||||

| 19 | ALE Low to Valid Data In |

| at 12MHz | tALLVD |

| 8tCLK - 150 | ns | |||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| at 16MHz |

| 8tCLK - 90 | |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

| 20 | Valid Address to Valid Data In | at 12MHz | tAVDV |

| 9tCLK - 165 | ns | ||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| at 16MHz |

| 9tCLK - 105 | ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

| 21 | ALE Low to |

|

| or |

|

|

| Low |

|

|

| tALLRDL | 3tCLK - 50 | 3tCLK + 50 | ns | |||||||||||||||||||||

RD | WR |

|

|

| |||||||||||||||||||||||||||||||||

| 22 | Address Valid to |

|

|

|

|

| or |

|

| Low | tAVRDL | 4tCLK - 130 |

| ns | ||||||||||||||||||||||

RD | WR |

| |||||||||||||||||||||||||||||||||||

| 23 | Data Valid to |

|

|

|

|

| Going Low |

|

|

| tDVWRL | tCLK - 60 |

| ns | ||||||||||||||||||||||

WR |

|

|

|

| |||||||||||||||||||||||||||||||||

|

| Data Valid to |

|

|

|

|

| High |

| at 12MHz |

| 7tCLK - 150 |

|

| |||||||||||||||||||||||

| 24 | WR |

| tDVWRH |

| ns | |||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| at 16MHz | 7tCLK - 90 |

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

| 25 | Data Valid After |

|

|

|

|

|

|

| High |

|

|

| tWRHDV | tCLK - 50 |

| ns | ||||||||||||||||||||

WR |

|

|

|

| |||||||||||||||||||||||||||||||||

| 26 |

|

|

| Low to Address Float |

|

|

| tRDLAZ |

| 0 | ns | |||||||||||||||||||||||||

| RD |

|

|

|

| ||||||||||||||||||||||||||||||||

| 27 |

|

|

|

| or |

| High to ALE High |

|

|

| tRDHALH | tCLK - 40 | tCLK + 50 | ns | ||||||||||||||||||||||

| RD | WR |

|

|

| ||||||||||||||||||||||||||||||||

13 of 26