DS5001FP

INSTRUCTION SET

The DS5001FP executes an instruction set that is object

MEMORY ORGANIZATION

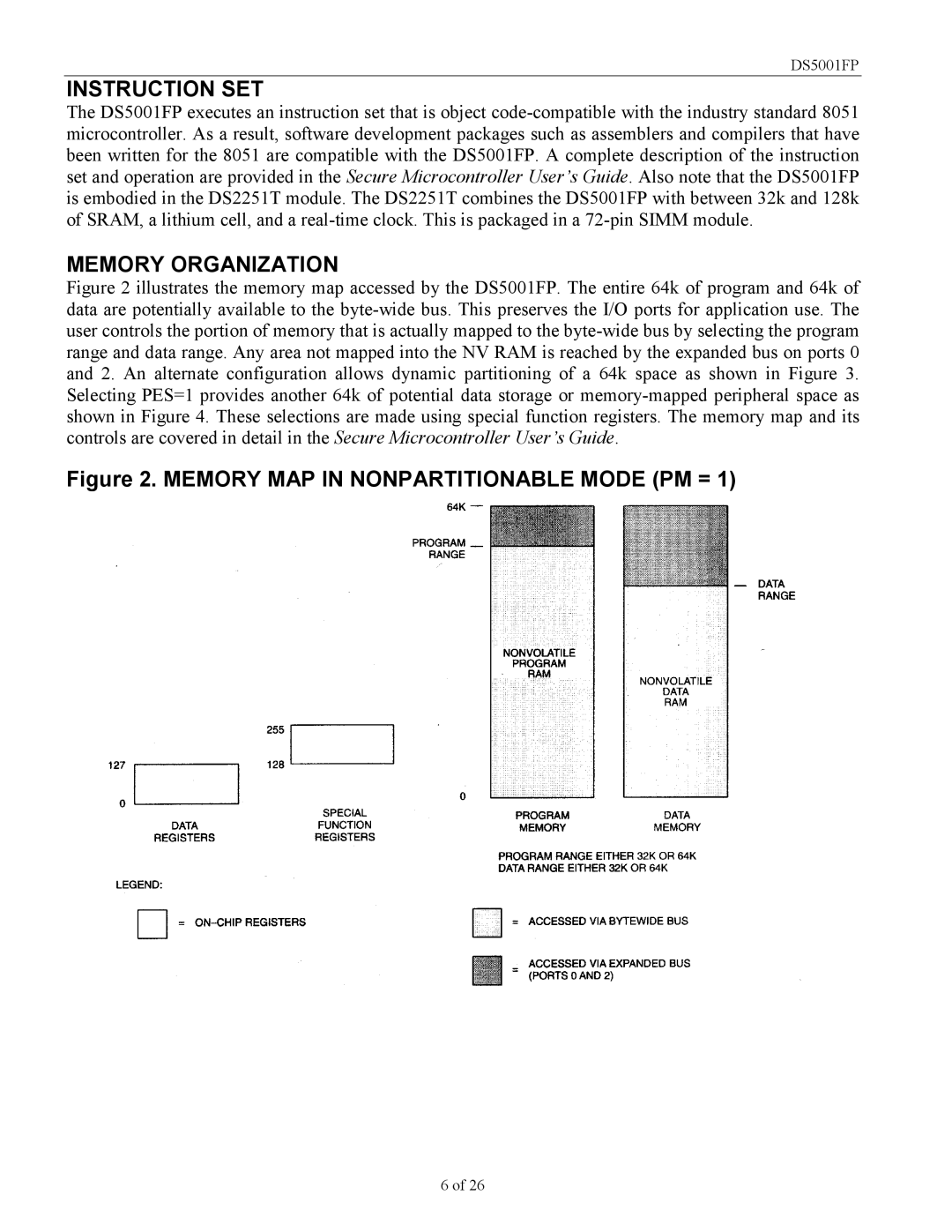

Figure 2 illustrates the memory map accessed by the DS5001FP. The entire 64k of program and 64k of data are potentially available to the byte-wide bus. This preserves the I/O ports for application use. The user controls the portion of memory that is actually mapped to the byte-wide bus by selecting the program range and data range. Any area not mapped into the NV RAM is reached by the expanded bus on ports 0 and 2. An alternate configuration allows dynamic partitioning of a 64k space as shown in Figure 3. Selecting PES=1 provides another 64k of potential data storage or memory-mapped peripheral space as shown in Figure 4. These selections are made using special function registers. The memory map and its controls are covered in detail in the Secure Microcontroller User’s Guide.

Figure 2. MEMORY MAP IN NONPARTITIONABLE MODE (PM = 1)

6 of 26