BIOS Setup

AGP Master 1 WS Write

When Enabled is selected , writes to the AGP bus are executed with one wait state inserted.

AGP Master 1 WS Read

When Enabled is selected, one wait state is inserted in the AGP read cycle.

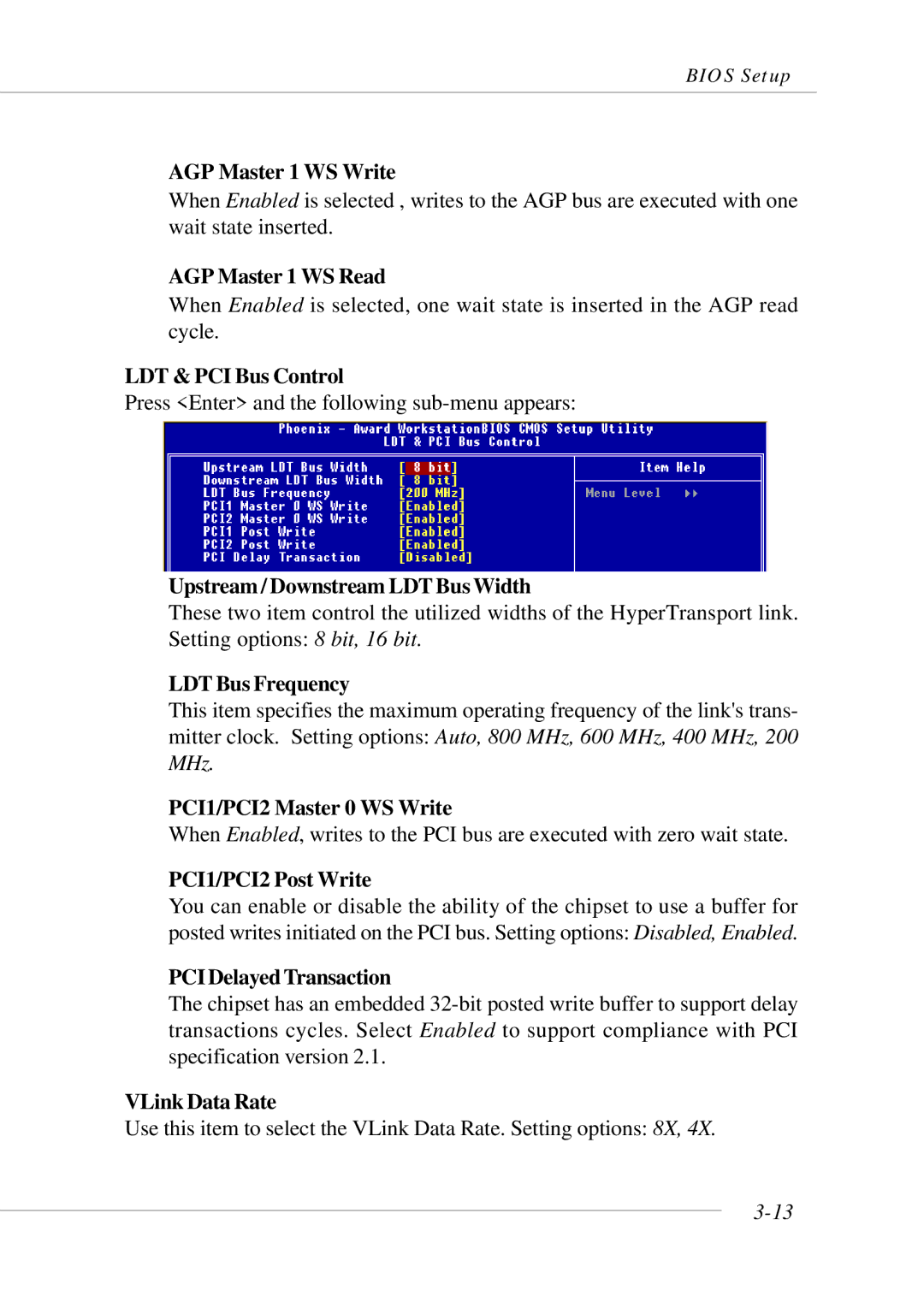

LDT & PCI Bus Control

Press <Enter> and the following

Upstream / Downstream LDT Bus Width

These two item control the utilized widths of the HyperTransport link. Setting options: 8 bit, 16 bit.

LDT Bus Frequency

This item specifies the maximum operating frequency of the link's trans- mitter clock. Setting options: Auto, 800 MHz, 600 MHz, 400 MHz, 200 MHz.

PCI1/PCI2 Master 0 WS Write

When Enabled, writes to the PCI bus are executed with zero wait state.

PCI1/PCI2 Post Write

You can enable or disable the ability of the chipset to use a buffer for posted writes initiated on the PCI bus. Setting options: Disabled, Enabled.

PCI Delayed Transaction

The chipset has an embedded

VLink Data Rate

Use this item to select the VLink Data Rate. Setting options: 8X, 4X.