September 2006

DS90C3202

3.3V 8 MHz to 135 MHz Dual FPD-Link Receiver

DS90C3202 3.

General Description

The DS90C3202 is a 3.3V single/dual

Features

nUp to 9.45 Gbit/s data throughput

n8 MHz to 135 MHz input clock support n Supports up to QXGA panel resolutions

n Supports HDTV panel resolutions and frame rates up to 1920 x 1080p

n LVDS

n

n Programmable clock edge and control strobe select n Power down mode

n +3.3V supply voltage

n

n Compliant to

3V 8 MHz to 135 MHz Dual

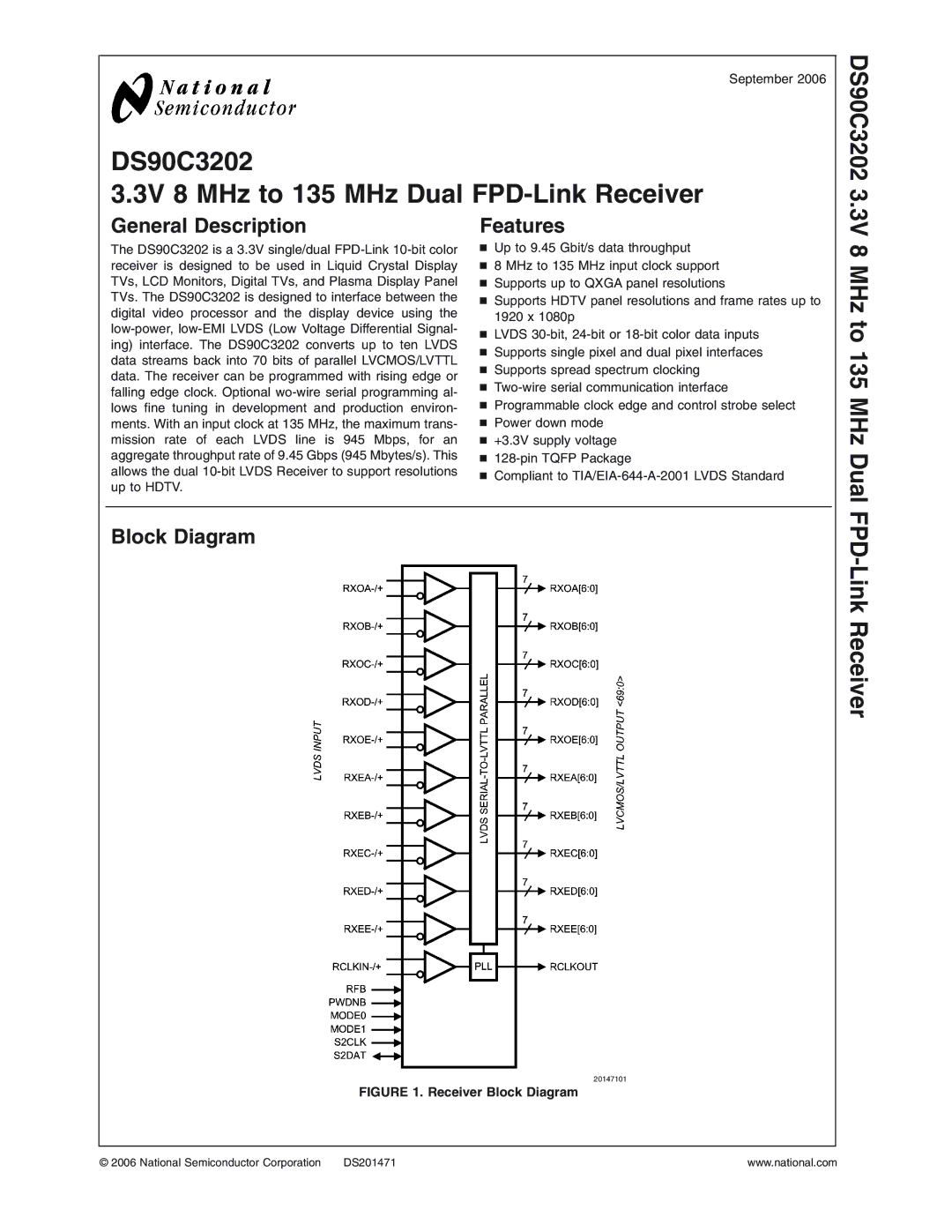

Block Diagram

20147101

FIGURE 1. Receiver Block Diagram

FPD-Link Receiver

© 2006 National Semiconductor Corporation | DS201471 | www.national.com |