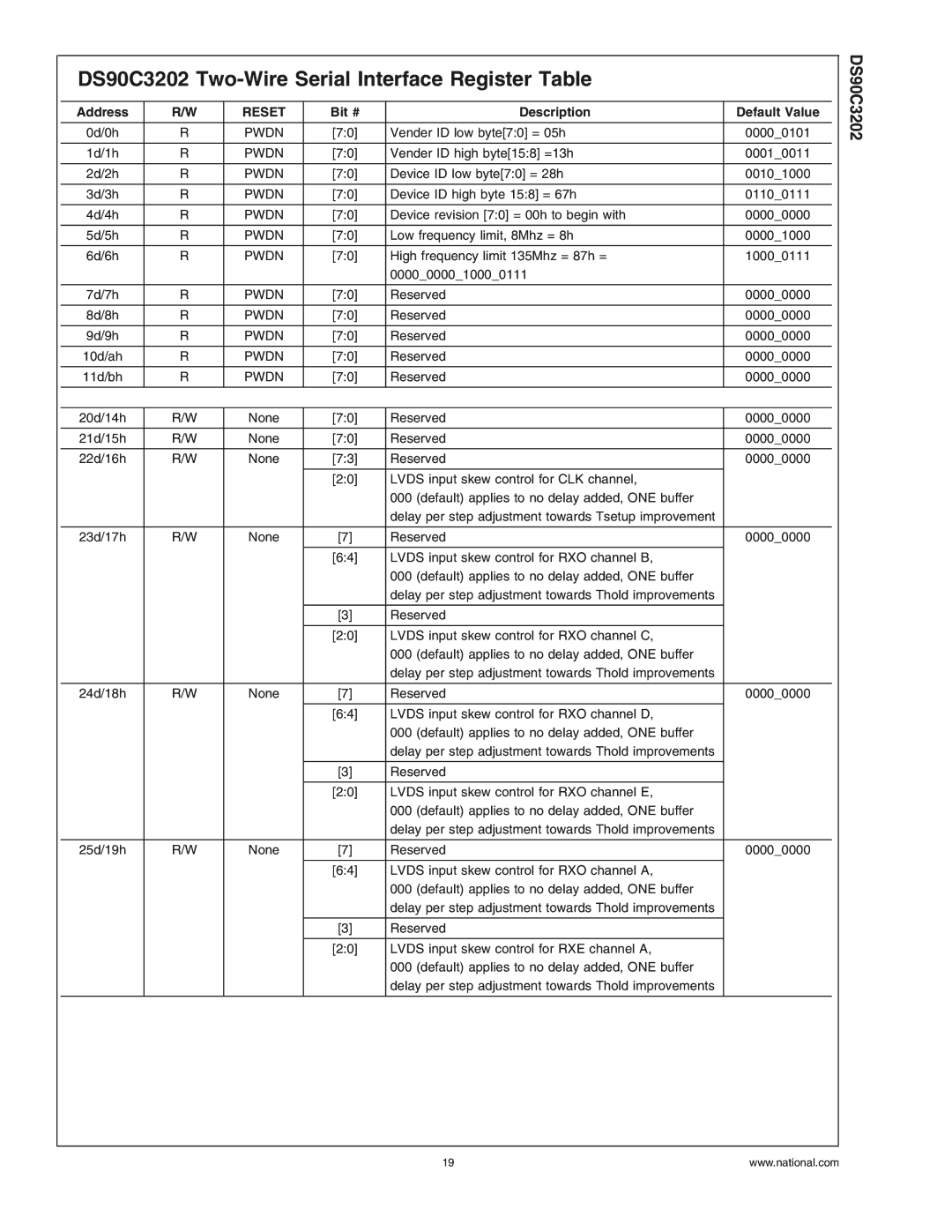

DS90C3202 Two-Wire Serial Interface Register Table

Address | R/W | RESET | Bit # | Description | Default Value |

|

|

|

|

|

|

0d/0h | R | PWDN | [7:0] | Vender ID low byte[7:0] = 05h | 0000_0101 |

|

|

|

|

|

|

1d/1h | R | PWDN | [7:0] | Vender ID high byte[15:8] =13h | 0001_0011 |

|

|

|

|

|

|

2d/2h | R | PWDN | [7:0] | Device ID low byte[7:0] = 28h | 0010_1000 |

|

|

|

|

|

|

3d/3h | R | PWDN | [7:0] | Device ID high byte 15:8] = 67h | 0110_0111 |

|

|

|

|

|

|

4d/4h | R | PWDN | [7:0] | Device revision [7:0] = 00h to begin with | 0000_0000 |

|

|

|

|

|

|

5d/5h | R | PWDN | [7:0] | Low frequency limit, 8Mhz = 8h | 0000_1000 |

|

|

|

|

|

|

6d/6h | R | PWDN | [7:0] | High frequency limit 135Mhz = 87h = | 1000_0111 |

|

|

|

| 0000_0000_1000_0111 |

|

|

|

|

|

|

|

7d/7h | R | PWDN | [7:0] | Reserved | 0000_0000 |

|

|

|

|

|

|

8d/8h | R | PWDN | [7:0] | Reserved | 0000_0000 |

|

|

|

|

|

|

9d/9h | R | PWDN | [7:0] | Reserved | 0000_0000 |

|

|

|

|

|

|

10d/ah | R | PWDN | [7:0] | Reserved | 0000_0000 |

|

|

|

|

|

|

11d/bh | R | PWDN | [7:0] | Reserved | 0000_0000 |

|

|

|

|

|

|

|

|

|

|

|

|

20d/14h | R/W | None | [7:0] | Reserved | 0000_0000 |

|

|

|

|

|

|

21d/15h | R/W | None | [7:0] | Reserved | 0000_0000 |

|

|

|

|

|

|

22d/16h | R/W | None | [7:3] | Reserved | 0000_0000 |

|

|

|

|

|

|

|

|

| [2:0] | LVDS input skew control for CLK channel, |

|

|

|

|

| 000 (default) applies to no delay added, ONE buffer |

|

|

|

|

| delay per step adjustment towards Tsetup improvement |

|

|

|

|

|

|

|

23d/17h | R/W | None | [7] | Reserved | 0000_0000 |

|

|

|

|

|

|

|

|

| [6:4] | LVDS input skew control for RXO channel B, |

|

|

|

|

| 000 (default) applies to no delay added, ONE buffer |

|

|

|

|

| delay per step adjustment towards Thold improvements |

|

|

|

|

|

|

|

|

|

| [3] | Reserved |

|

|

|

|

|

|

|

|

|

| [2:0] | LVDS input skew control for RXO channel C, |

|

|

|

|

| 000 (default) applies to no delay added, ONE buffer |

|

|

|

|

| delay per step adjustment towards Thold improvements |

|

|

|

|

|

|

|

24d/18h | R/W | None | [7] | Reserved | 0000_0000 |

|

|

|

|

|

|

|

|

| [6:4] | LVDS input skew control for RXO channel D, |

|

|

|

|

| 000 (default) applies to no delay added, ONE buffer |

|

|

|

|

| delay per step adjustment towards Thold improvements |

|

|

|

|

|

|

|

|

|

| [3] | Reserved |

|

|

|

|

|

|

|

|

|

| [2:0] | LVDS input skew control for RXO channel E, |

|

|

|

|

| 000 (default) applies to no delay added, ONE buffer |

|

|

|

|

| delay per step adjustment towards Thold improvements |

|

|

|

|

|

|

|

25d/19h | R/W | None | [7] | Reserved | 0000_0000 |

|

|

|

|

|

|

|

|

| [6:4] | LVDS input skew control for RXO channel A, |

|

|

|

|

| 000 (default) applies to no delay added, ONE buffer |

|

|

|

|

| delay per step adjustment towards Thold improvements |

|

|

|

|

|

|

|

|

|

| [3] | Reserved |

|

|

|

|

|

|

|

|

|

| [2:0] | LVDS input skew control for RXE channel A, |

|

|

|

|

| 000 (default) applies to no delay added, ONE buffer |

|

|

|

|

| delay per step adjustment towards Thold improvements |

|

|

|

|

|

|

|

DS90C3202

19 | www.national.com |