Code | Description |

|

|

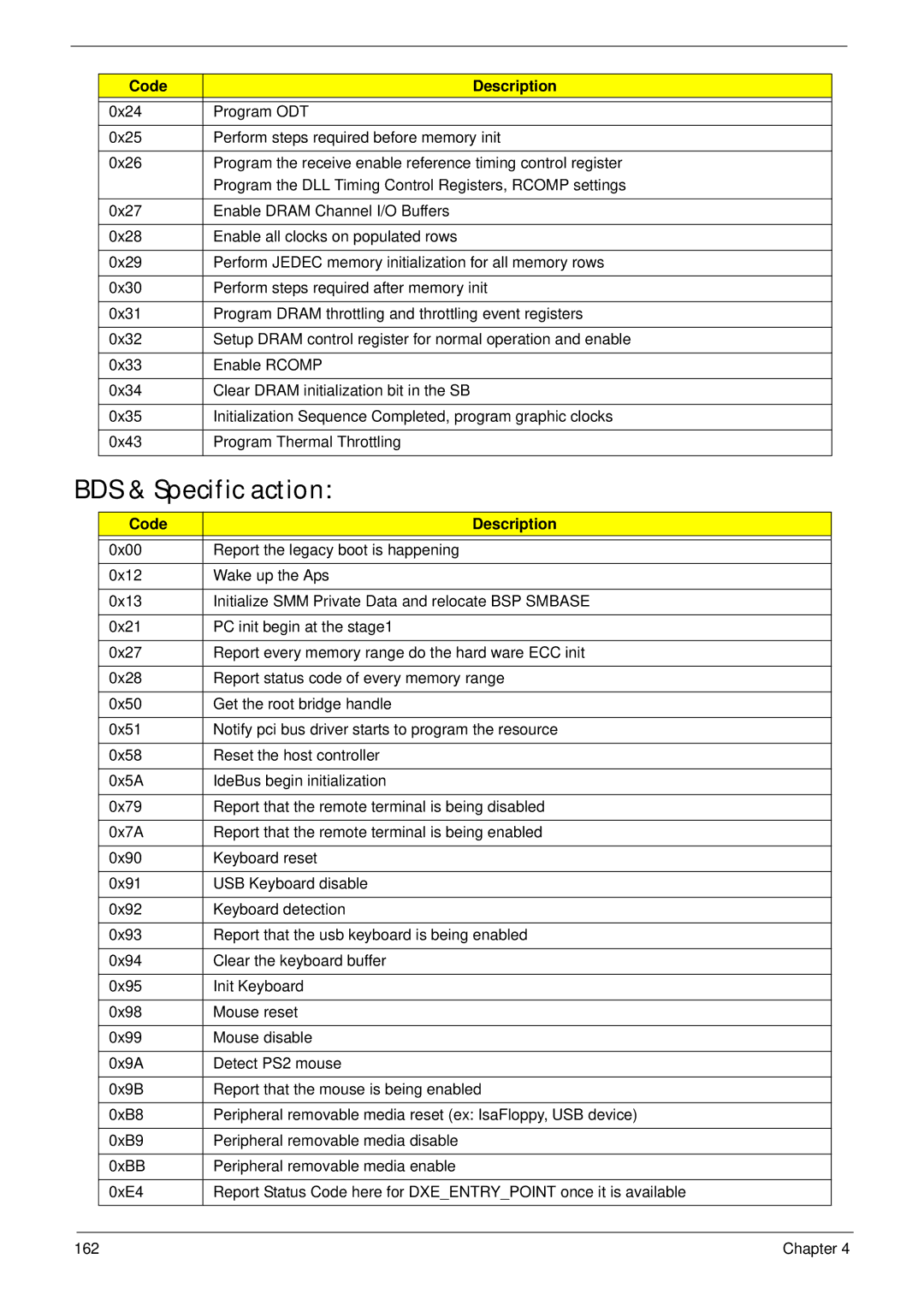

0x24 | Program ODT |

0x25 | Perform steps required before memory init |

|

|

0x26 | Program the receive enable reference timing control register |

| Program the DLL Timing Control Registers, RCOMP settings |

|

|

0x27 | Enable DRAM Channel I/O Buffers |

|

|

0x28 | Enable all clocks on populated rows |

|

|

0x29 | Perform JEDEC memory initialization for all memory rows |

|

|

0x30 | Perform steps required after memory init |

|

|

0x31 | Program DRAM throttling and throttling event registers |

|

|

0x32 | Setup DRAM control register for normal operation and enable |

|

|

0x33 | Enable RCOMP |

|

|

0x34 | Clear DRAM initialization bit in the SB |

|

|

0x35 | Initialization Sequence Completed, program graphic clocks |

|

|

0x43 | Program Thermal Throttling |

|

|

BDS & Specific action:

Code | Description |

|

|

0x00 | Report the legacy boot is happening |

|

|

0x12 | Wake up the Aps |

|

|

0x13 | Initialize SMM Private Data and relocate BSP SMBASE |

|

|

0x21 | PC init begin at the stage1 |

|

|

0x27 | Report every memory range do the hard ware ECC init |

|

|

0x28 | Report status code of every memory range |

|

|

0x50 | Get the root bridge handle |

|

|

0x51 | Notify pci bus driver starts to program the resource |

|

|

0x58 | Reset the host controller |

|

|

0x5A | IdeBus begin initialization |

|

|

0x79 | Report that the remote terminal is being disabled |

|

|

0x7A | Report that the remote terminal is being enabled |

|

|

0x90 | Keyboard reset |

|

|

0x91 | USB Keyboard disable |

|

|

0x92 | Keyboard detection |

|

|

0x93 | Report that the usb keyboard is being enabled |

|

|

0x94 | Clear the keyboard buffer |

|

|

0x95 | Init Keyboard |

|

|

0x98 | Mouse reset |

|

|

0x99 | Mouse disable |

|

|

0x9A | Detect PS2 mouse |

|

|

0x9B | Report that the mouse is being enabled |

|

|

0xB8 | Peripheral removable media reset (ex: IsaFloppy, USB device) |

|

|

0xB9 | Peripheral removable media disable |

|

|

0xBB | Peripheral removable media enable |

|

|

0xE4 | Report Status Code here for DXE_ENTRY_POINT once it is available |

|

|

162 | Chapter 4 |