BIT |

| DESCRIPTION | |

|

| ||

7 | FFE | ||

| When logic 1, indicates FIFO mode enabled. Always logic 0 for the 16450. | ||

6 | FFE | ||

| When logic 1, indicates FIFO mode enabled. Always logic 0 for the 16450. | ||

5 | 0 | ||

|

| ||

4 | 0 | ||

|

| ||

3 | IID2 | ||

2 | IID1 | Indicates highest priority interrupt pending if any. See Figure 16. | |

NOTE: IID2 is always a logic 0 on the 16450 or in | |||

1 | IID0 | ||

| |||

|

| ||

0 | IP | ||

| When logic 0, indicates that an interrupt is pending and the contents of the interrupt | ||

| identification register may be used to determine the interrupt source. See Figure 16. | ||

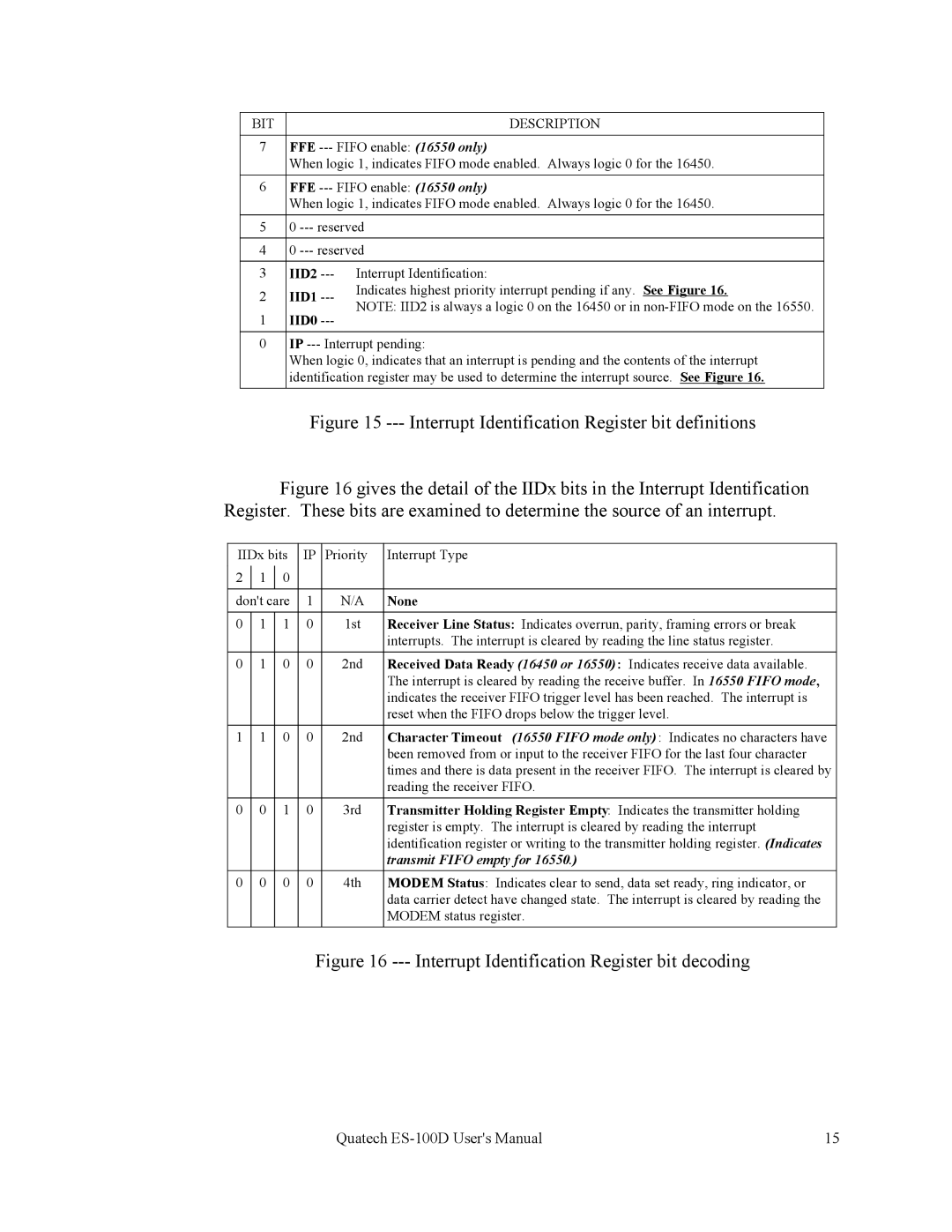

| Figure 15 | ||

Figure 16 gives the detail of the IIDx bits in the Interrupt Identification Register. These bits are examined to determine the source of an interrupt.

IIDx bits | IP | Priority | Interrupt Type | |||

2 |

| 0 |

|

|

|

|

1 |

|

|

|

| ||

|

|

|

|

|

| |

don't care | 1 | N/A | None | |||

0 | 1 | 1 | 0 | 1st | Receiver Line Status: Indicates overrun, parity, framing errors or break | |

|

|

|

|

| interrupts. The interrupt is cleared by reading the line status register. | |

0 | 1 | 0 | 0 | 2nd | Received Data Ready (16450 or 16550): Indicates receive data available. | |

|

|

|

|

| The interrupt is cleared by reading the receive buffer. In 16550 FIFO mode, | |

|

|

|

|

| indicates the receiver FIFO trigger level has been reached. The interrupt is | |

|

|

|

|

| reset when the FIFO drops below the trigger level. | |

1 | 1 | 0 | 0 | 2nd | Character Timeout (16550 FIFO mode only): Indicates no characters have | |

|

|

|

|

| been removed from or input to the receiver FIFO for the last four character | |

|

|

|

|

| times and there is data present in the receiver FIFO. The interrupt is cleared by | |

|

|

|

|

| reading the receiver FIFO. | |

0 | 0 | 1 | 0 | 3rd | Transmitter Holding Register Empty: Indicates the transmitter holding | |

|

|

|

|

| register is empty. The interrupt is cleared by reading the interrupt | |

|

|

|

|

| identification register or writing to the transmitter holding register. (Indicates | |

|

|

|

|

| transmit FIFO empty for 16550.) | |

0 | 0 | 0 | 0 | 4th | MODEM Status: Indicates clear to send, data set ready, ring indicator, or | |

|

|

|

|

| data carrier detect have changed state. The interrupt is cleared by reading the | |

|

|

|

|

| MODEM status register. | |

|

|

| Figure 16 | Interrupt Identification Register bit decoding | ||

Quatech | 15 |