Accessing the Serial Port registers

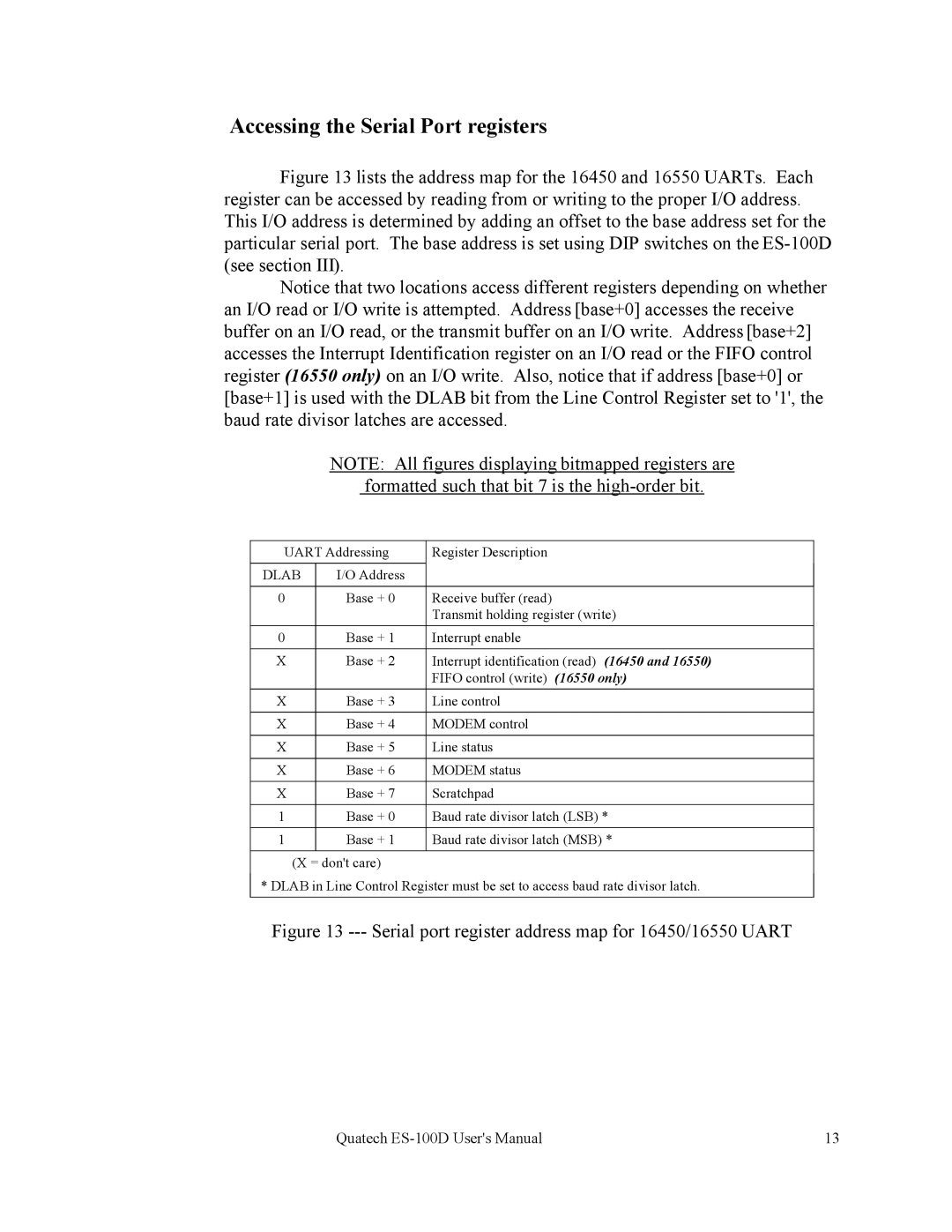

Figure 13 lists the address map for the 16450 and 16550 UARTs. Each register can be accessed by reading from or writing to the proper I/O address. This I/O address is determined by adding an offset to the base address set for the particular serial port. The base address is set using DIP switches on the ES-100D (see section III).

Notice that two locations access different registers depending on whether an I/O read or I/O write is attempted. Address [base+0] accesses the receive buffer on an I/O read, or the transmit buffer on an I/O write. Address [base+2] accesses the Interrupt Identification register on an I/O read or the FIFO control register (16550 only) on an I/O write. Also, notice that if address [base+0] or [base+1] is used with the DLAB bit from the Line Control Register set to '1', the baud rate divisor latches are accessed.

NOTE: All figures displaying bitmapped registers are formatted such that bit 7 is the

UART Addressing | Register Description | |

DLAB | I/O Address |

|

|

|

|

0 | Base + 0 | Receive buffer (read) |

|

| Transmit holding register (write) |

0 | Base + 1 | Interrupt enable |

|

|

|

X | Base + 2 | Interrupt identification (read) (16450 and 16550) |

|

| FIFO control (write) (16550 only) |

X | Base + 3 | Line control |

|

|

|

X | Base + 4 | MODEM control |

|

|

|

X | Base + 5 | Line status |

|

|

|

X | Base + 6 | MODEM status |

X | Base + 7 | Scratchpad |

|

|

|

1 | Base + 0 | Baud rate divisor latch (LSB) * |

|

|

|

1 | Base + 1 | Baud rate divisor latch (MSB) * |

|

|

|

(X = don't care)

* DLAB in Line Control Register must be set to access baud rate divisor latch.

Figure 13 --- Serial port register address map for 16450/16550 UART

Quatech | 13 |