LINE STATUS REGISTER

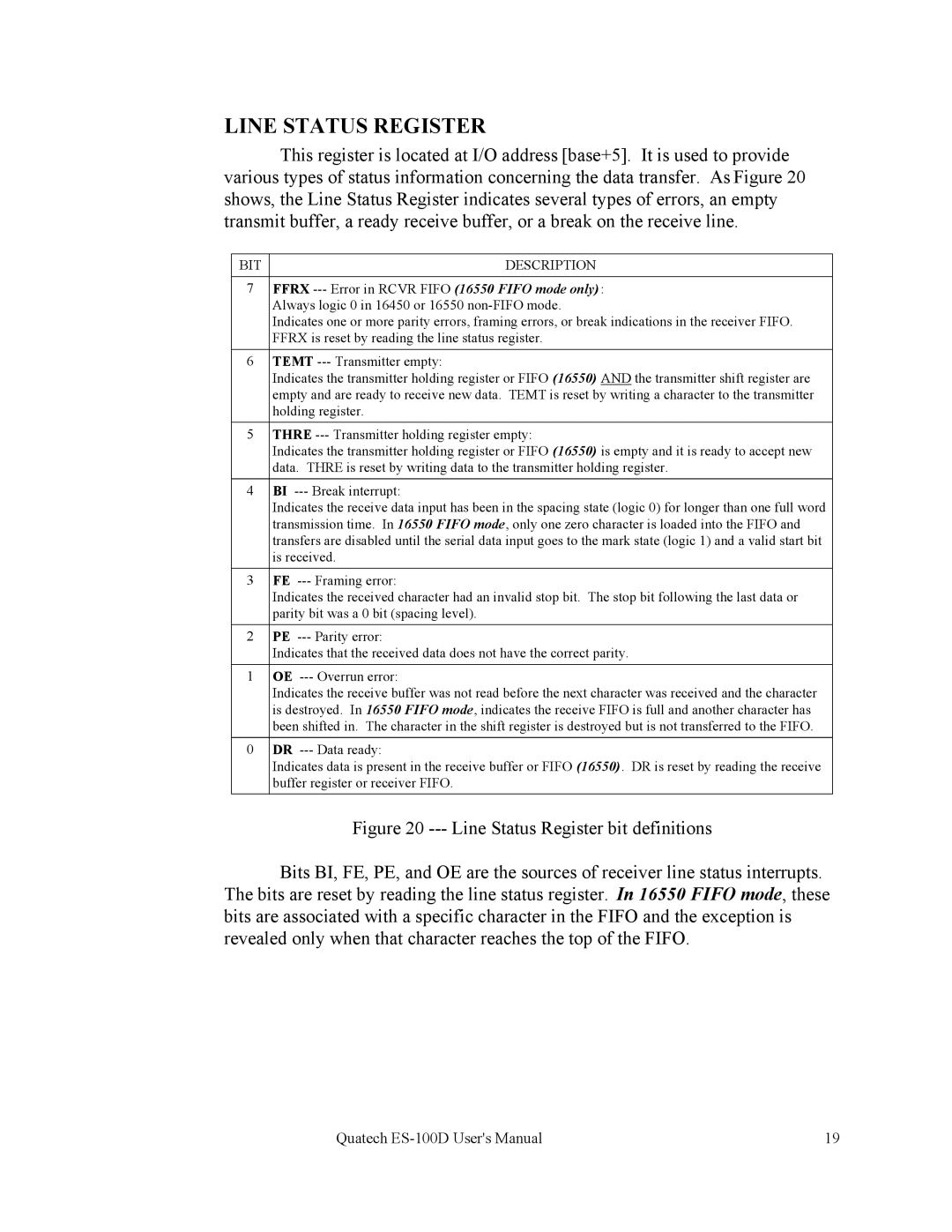

This register is located at I/O address [base+5]. It is used to provide various types of status information concerning the data transfer. As Figure 20 shows, the Line Status Register indicates several types of errors, an empty transmit buffer, a ready receive buffer, or a break on the receive line.

BIT | DESCRIPTION |

|

|

7 | FFRX |

| Always logic 0 in 16450 or 16550 |

| Indicates one or more parity errors, framing errors, or break indications in the receiver FIFO. |

| FFRX is reset by reading the line status register. |

6 | TEMT |

| Indicates the transmitter holding register or FIFO (16550) AND the transmitter shift register are |

| empty and are ready to receive new data. TEMT is reset by writing a character to the transmitter |

| holding register. |

5 | THRE |

| Indicates the transmitter holding register or FIFO (16550) is empty and it is ready to accept new |

| data. THRE is reset by writing data to the transmitter holding register. |

4 | BI |

| Indicates the receive data input has been in the spacing state (logic 0) for longer than one full word |

| transmission time. In 16550 FIFO mode, only one zero character is loaded into the FIFO and |

| transfers are disabled until the serial data input goes to the mark state (logic 1) and a valid start bit |

| is received. |

3 | FE |

| Indicates the received character had an invalid stop bit. The stop bit following the last data or |

| parity bit was a 0 bit (spacing level). |

2 | PE |

| Indicates that the received data does not have the correct parity. |

1 | OE |

| Indicates the receive buffer was not read before the next character was received and the character |

| is destroyed. In 16550 FIFO mode, indicates the receive FIFO is full and another character has |

| been shifted in. The character in the shift register is destroyed but is not transferred to the FIFO. |

0 | DR |

| Indicates data is present in the receive buffer or FIFO (16550). DR is reset by reading the receive |

| buffer register or receiver FIFO. |

| Figure 20 |

Bits BI, FE, PE, and OE are the sources of receiver line status interrupts. The bits are reset by reading the line status register. In 16550 FIFO mode, these bits are associated with a specific character in the FIFO and the exception is revealed only when that character reaches the top of the FIFO.

Quatech | 19 |