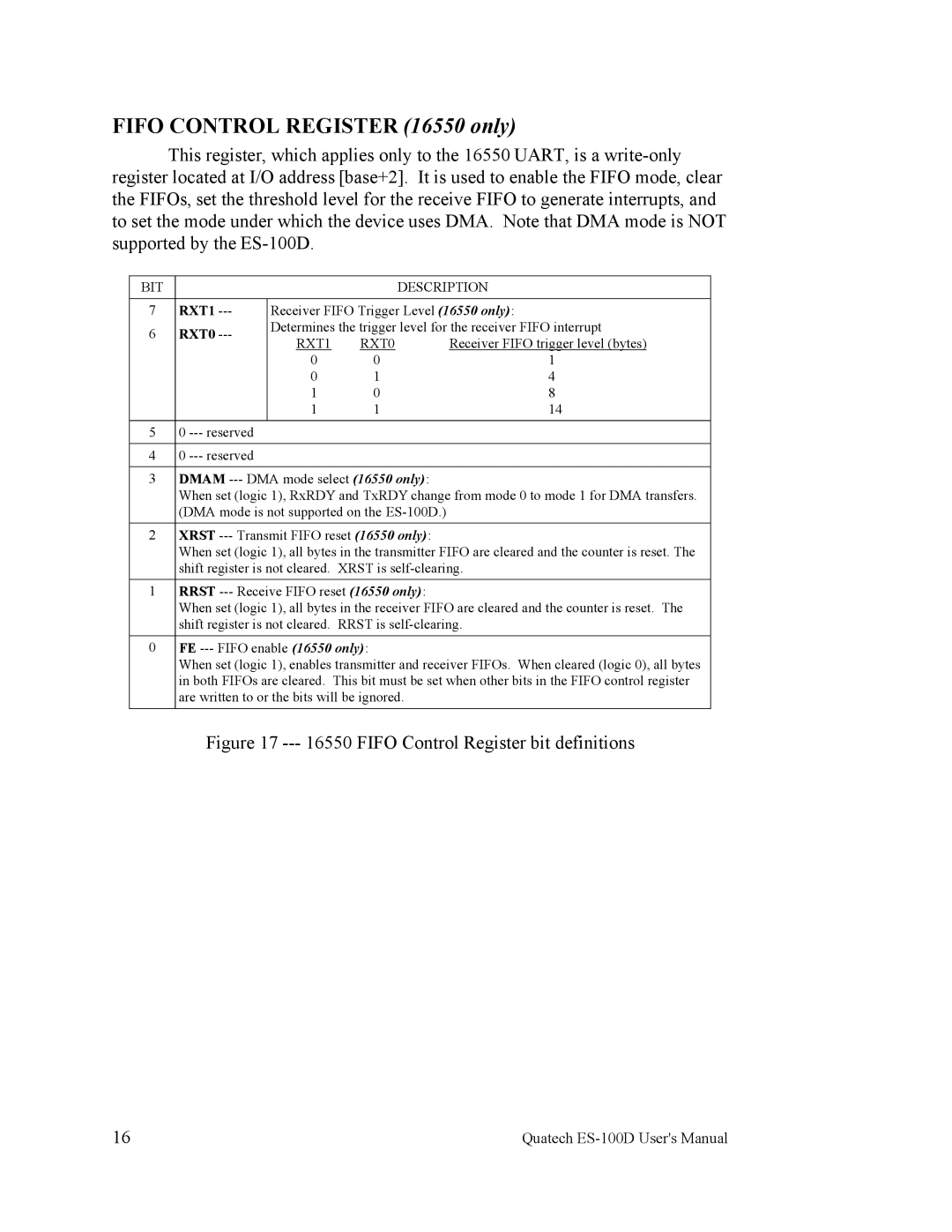

FIFO CONTROL REGISTER (16550 only)

This register, which applies only to the 16550 UART, is a

BIT |

|

| DESCRIPTION | ||

|

|

| |||

7 | RXT1 | Receiver FIFO Trigger Level (16550 only): | |||

6 | RXT0 | Determines the trigger level for the receiver FIFO interrupt | |||

RXT1 | RXT0 | Receiver FIFO trigger level (bytes) | |||

|

| ||||

|

| 0 | 0 | 1 | |

|

| 0 | 1 | 4 | |

|

| 1 | 0 | 8 | |

|

| 1 | 1 | 14 | |

5 | 0 |

|

|

| |

|

|

|

|

| |

4 | 0 |

|

|

| |

|

|

|

| ||

3 | DMAM |

| |||

| When set (logic 1), RxRDY and TxRDY change from mode 0 to mode 1 for DMA transfers. | ||||

| (DMA mode is not supported on the |

| |||

2 | XRST |

| |||

| When set (logic 1), all bytes in the transmitter FIFO are cleared and the counter is reset. The | ||||

| shift register is not cleared. XRST is | ||||

1 | RRST |

| |||

| When set (logic 1), all bytes in the receiver FIFO are cleared and the counter is reset. The | ||||

| shift register is not cleared. RRST is | ||||

0 | FE |

| |||

| When set (logic 1), enables transmitter and receiver FIFOs. When cleared (logic 0), all bytes | ||||

| in both FIFOs are cleared. This bit must be set when other bits in the FIFO control register | ||||

| are written to or the bits will be ignored. |

| |||

| Figure 17 | ||||

16 | Quatech |