S16A User’s Guide | Registers |

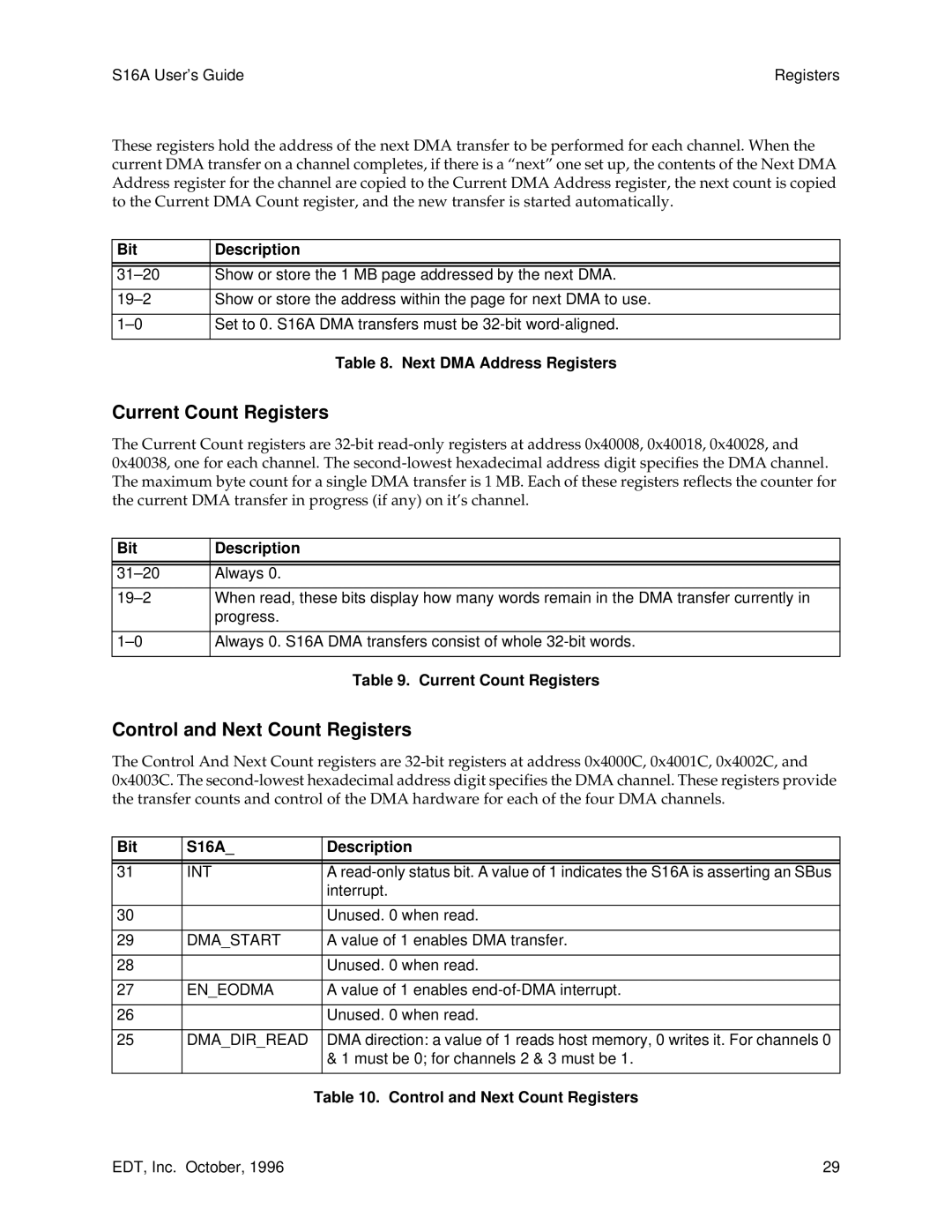

These registers hold the address of the next DMA transfer to be performed for each channel. When the current DMA transfer on a channel completes, if there is a “next” one set up, the contents of the Next DMA Address register for the channel are copied to the Current DMA Address register, the next count is copied to the Current DMA Count register, and the new transfer is started automatically.

Bit | Description |

|

|

|

|

Show or store the 1 MB page addressed by the next DMA. | |

|

|

Show or store the address within the page for next DMA to use. | |

|

|

Set to 0. S16A DMA transfers must be | |

|

|

Table 8. Next DMA Address Registers

Current Count Registers

The Current Count registers are

Bit | Description |

|

|

|

|

Always 0. | |

|

|

When read, these bits display how many words remain in the DMA transfer currently in | |

| progress. |

|

|

Always 0. S16A DMA transfers consist of whole | |

|

|

Table 9. Current Count Registers

Control and Next Count Registers

The Control And Next Count registers are

Bit | S16A_ |

| Description |

|

|

|

|

|

|

|

|

31 | INT |

| A |

|

|

| interrupt. |

|

|

|

|

30 |

|

| Unused. 0 when read. |

|

|

|

|

29 | DMA_START |

| A value of 1 enables DMA transfer. |

|

|

|

|

28 |

|

| Unused. 0 when read. |

|

|

|

|

27 | EN_EODMA |

| A value of 1 enables |

|

|

|

|

26 |

|

| Unused. 0 when read. |

|

|

|

|

25 | DMA_DIR_READ |

| DMA direction: a value of 1 reads host memory, 0 writes it. For channels 0 |

|

|

| & 1 must be 0; for channels 2 & 3 must be 1. |

|

|

|

|

|

| Table 10. Control and Next Count Registers | |

EDT, Inc. October, 1996 | 29 |