TS1G~32GCF133 |

| 133X CompactFlash Card | |||

|

|

|

|

|

|

|

|

|

|

| |

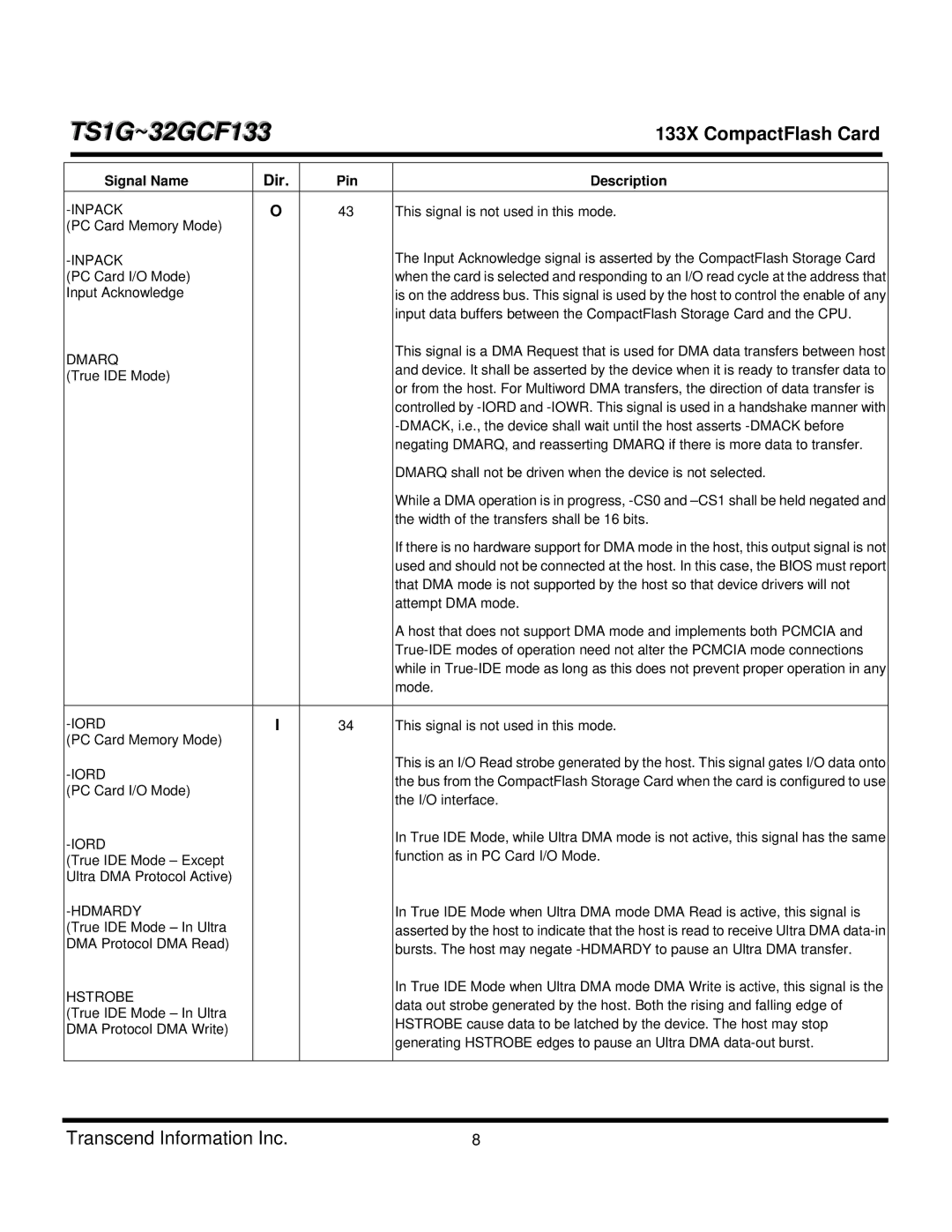

| Signal Name | Dir. | Pin | Description | |

| O | 43 | This signal is not used in this mode. | ||

(PC Card Memory Mode) |

|

|

|

| |

|

| The Input Acknowledge signal is asserted by the CompactFlash Storage Card | |||

(PC Card I/O Mode) |

|

| when the card is selected and responding to an I/O read cycle at the address that | ||

Input Acknowledge |

|

| is on the address bus. This signal is used by the host to control the enable of any | ||

|

|

|

| input data buffers between the CompactFlash Storage Card and the CPU. | |

DMARQ |

|

| This signal is a DMA Request that is used for DMA data transfers between host | ||

|

| and device. It shall be asserted by the device when it is ready to transfer data to | |||

(True IDE Mode) |

|

| |||

|

| or from the host. For Multiword DMA transfers, the direction of data transfer is | |||

|

|

|

| ||

|

|

|

| controlled by | |

|

|

|

| ||

|

|

|

| negating DMARQ, and reasserting DMARQ if there is more data to transfer. | |

|

|

|

| DMARQ shall not be driven when the device is not selected. | |

|

|

|

| While a DMA operation is in progress, | |

|

|

|

| the width of the transfers shall be 16 bits. | |

|

|

|

| If there is no hardware support for DMA mode in the host, this output signal is not | |

|

|

|

| used and should not be connected at the host. In this case, the BIOS must report | |

|

|

|

| that DMA mode is not supported by the host so that device drivers will not | |

|

|

|

| attempt DMA mode. | |

|

|

|

| A host that does not support DMA mode and implements both PCMCIA and | |

|

|

|

| ||

|

|

|

| while in | |

|

|

|

| mode. | |

|

|

|

| ||

I | 34 | This signal is not used in this mode. | |||

(PC Card Memory Mode) |

|

|

|

| |

|

| This is an I/O Read strobe generated by the host. This signal gates I/O data onto | |||

|

| the bus from the CompactFlash Storage Card when the card is configured to use | |||

(PC Card I/O Mode) |

|

| |||

|

| the I/O interface. | |||

|

|

|

| ||

|

| In True IDE Mode, while Ultra DMA mode is not active, this signal has the same | |||

|

| function as in PC Card I/O Mode. | |||

(True IDE Mode – Except |

|

| |||

Ultra DMA Protocol Active) |

|

|

|

| |

|

|

| In True IDE Mode when Ultra DMA mode DMA Read is active, this signal is | ||

(True IDE Mode – In Ultra |

|

| asserted by the host to indicate that the host is read to receive Ultra DMA | ||

DMA Protocol DMA Read) |

|

| bursts. The host may negate | ||

|

|

|

| ||

HSTROBE |

|

| In True IDE Mode when Ultra DMA mode DMA Write is active, this signal is the | ||

|

| data out strobe generated by the host. Both the rising and falling edge of | |||

(True IDE Mode – In Ultra |

|

| |||

|

| HSTROBE cause data to be latched by the device. The host may stop | |||

DMA Protocol DMA Write) |

|

| |||

|

| generating HSTROBE edges to pause an Ultra DMA | |||

|

|

|

| ||

|

|

|

|

|

|

Transcend Information Inc. | 8 |