Chapter 4: Detailed Example Design

simulation/timing

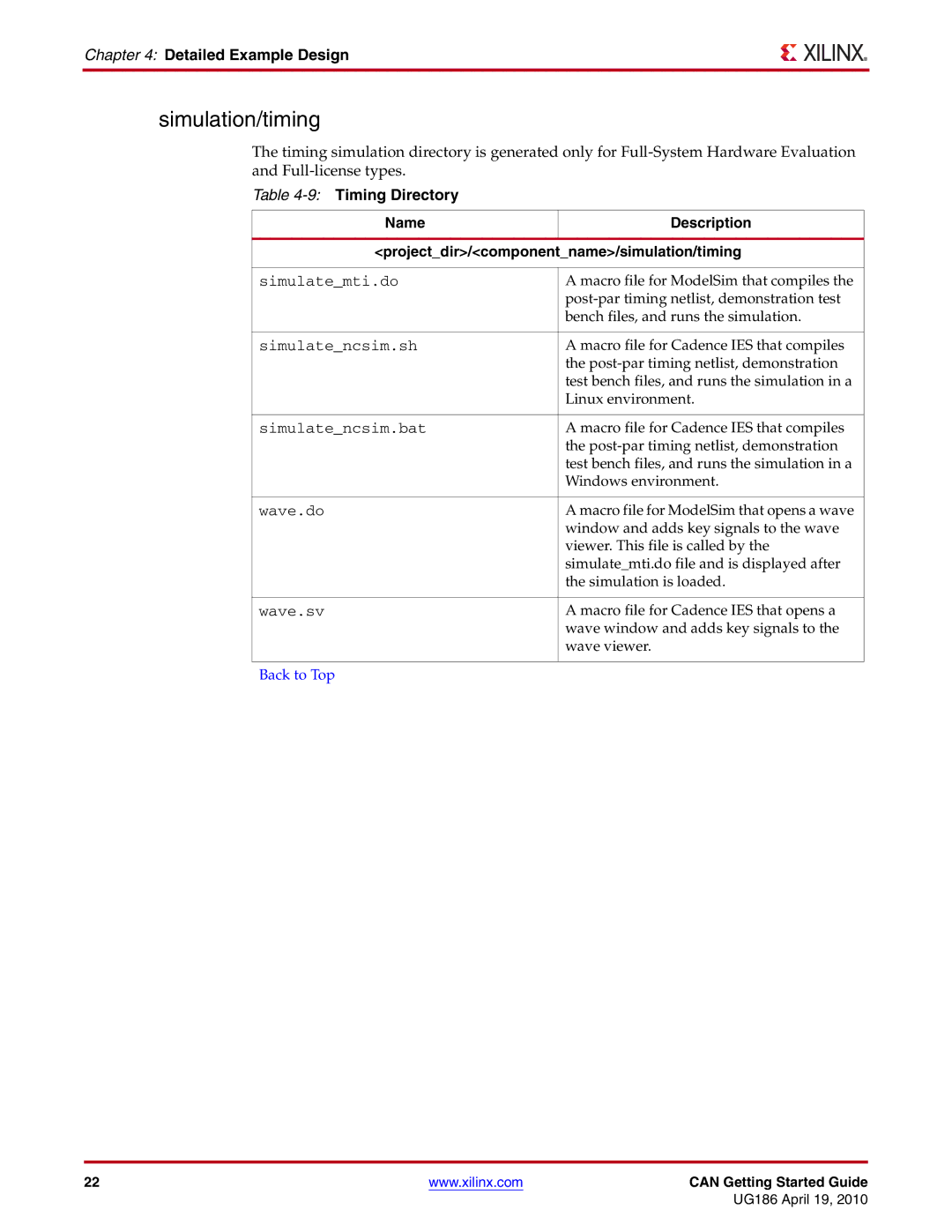

The timing simulation directory is generated only for

Table

Name | Description |

|

|

<project_dir>/<component_name>/simulation/timing | |

|

|

simulate_mti.do | A macro file for ModelSim that compiles the |

| |

| bench files, and runs the simulation. |

|

|

simulate_ncsim.sh | A macro file for Cadence IES that compiles |

| the |

| test bench files, and runs the simulation in a |

| Linux environment. |

|

|

simulate_ncsim.bat | A macro file for Cadence IES that compiles |

| the |

| test bench files, and runs the simulation in a |

| Windows environment. |

|

|

wave.do | A macro file for ModelSim that opens a wave |

| window and adds key signals to the wave |

| viewer. This file is called by the |

| simulate_mti.do file and is displayed after |

| the simulation is loaded. |

|

|

wave.sv | A macro file for Cadence IES that opens a |

| wave window and adds key signals to the |

| wave viewer. |

|

|

Back to Top |

|

22 | www.xilinx.com | CAN Getting Started Guide |

|

| UG186 April 19, 2010 |