Chapter 4: Detailed Example Design

Timing Simulation

Note: Present only with a Full license.

The test scripts are a ModelSim or a Cadence IES macro that automates the simulation of the test bench. They are located in:

<project_dir>/<component_name>/simulation/timing/

The test script performs the following tasks:

•Compiles the SimPrim based gate level netlist simulation model

•Compiles the demonstration test bench

•Starts a simulation of the test bench

•Opens a Wave window and adds signals of interest (wave_mti.do/wave_ncsim.sv)

•Runs the simulation to completion

Example Design Configuration

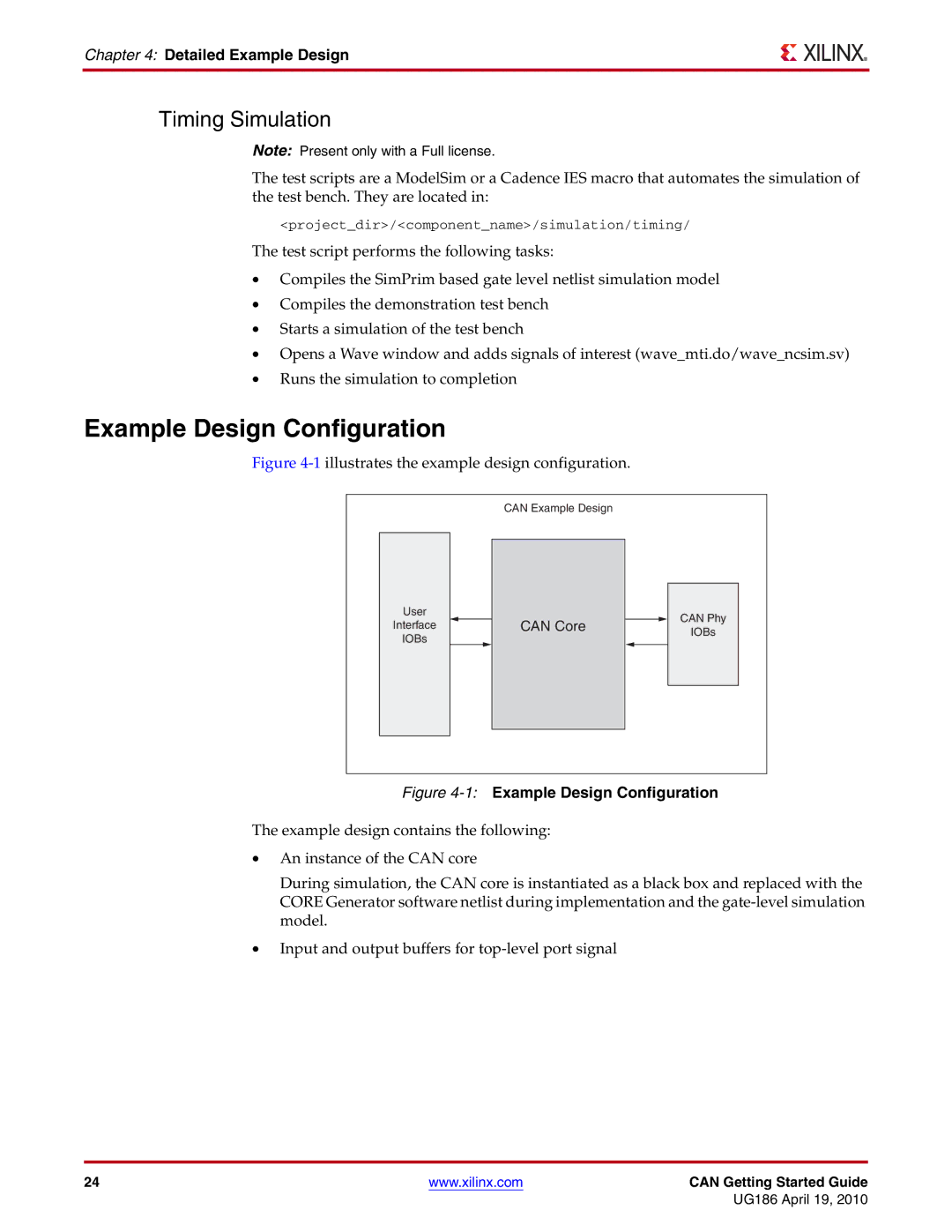

Figure 4-1 illustrates the example design configuration.

| CAN Example Design |

| |

User |

| CAN Phy | |

Interface | CAN Core | ||

IOBs | |||

IOBs |

| ||

|

| ||

Figure | |||

The example design contains the following:

•An instance of the CAN core

During simulation, the CAN core is instantiated as a black box and replaced with the CORE Generator software netlist during implementation and the

•Input and output buffers for

24 | www.xilinx.com | CAN Getting Started Guide |

UG186 April 19, 2010