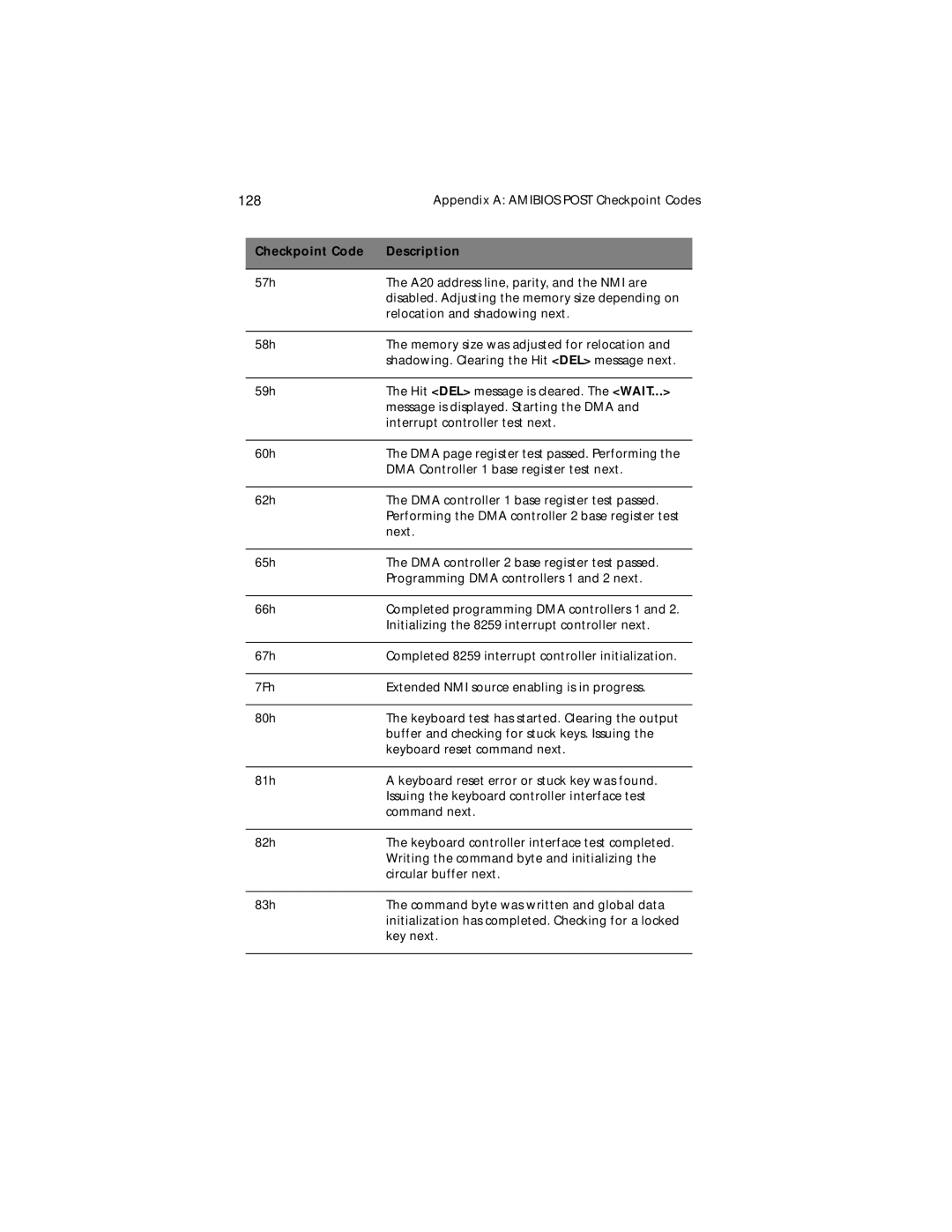

128 | Appendix A: AMIBIOS POST Checkpoint Codes |

Checkpoint Code | Description |

|

|

57h | The A20 address line, parity, and the NMI are |

| disabled. Adjusting the memory size depending on |

| relocation and shadowing next. |

|

|

58h | The memory size was adjusted for relocation and |

| shadowing. Clearing the Hit <DEL> message next. |

|

|

59h | The Hit <DEL> message is cleared. The <WAIT...> |

| message is displayed. Starting the DMA and |

| interrupt controller test next. |

|

|

60h | The DMA page register test passed. Performing the |

| DMA Controller 1 base register test next. |

|

|

62h | The DMA controller 1 base register test passed. |

| Performing the DMA controller 2 base register test |

| next. |

|

|

65h | The DMA controller 2 base register test passed. |

| Programming DMA controllers 1 and 2 next. |

|

|

66h | Completed programming DMA controllers 1 and 2. |

| Initializing the 8259 interrupt controller next. |

|

|

67h | Completed 8259 interrupt controller initialization. |

|

|

7Fh | Extended NMI source enabling is in progress. |

|

|

80h | The keyboard test has started. Clearing the output |

| buffer and checking for stuck keys. Issuing the |

| keyboard reset command next. |

|

|

81h | A keyboard reset error or stuck key was found. |

| Issuing the keyboard controller interface test |

| command next. |

|

|

82h | The keyboard controller interface test completed. |

| Writing the command byte and initializing the |

| circular buffer next. |

|

|

83h | The command byte was written and global data |

| initialization has completed. Checking for a locked |

| key next. |

|

|