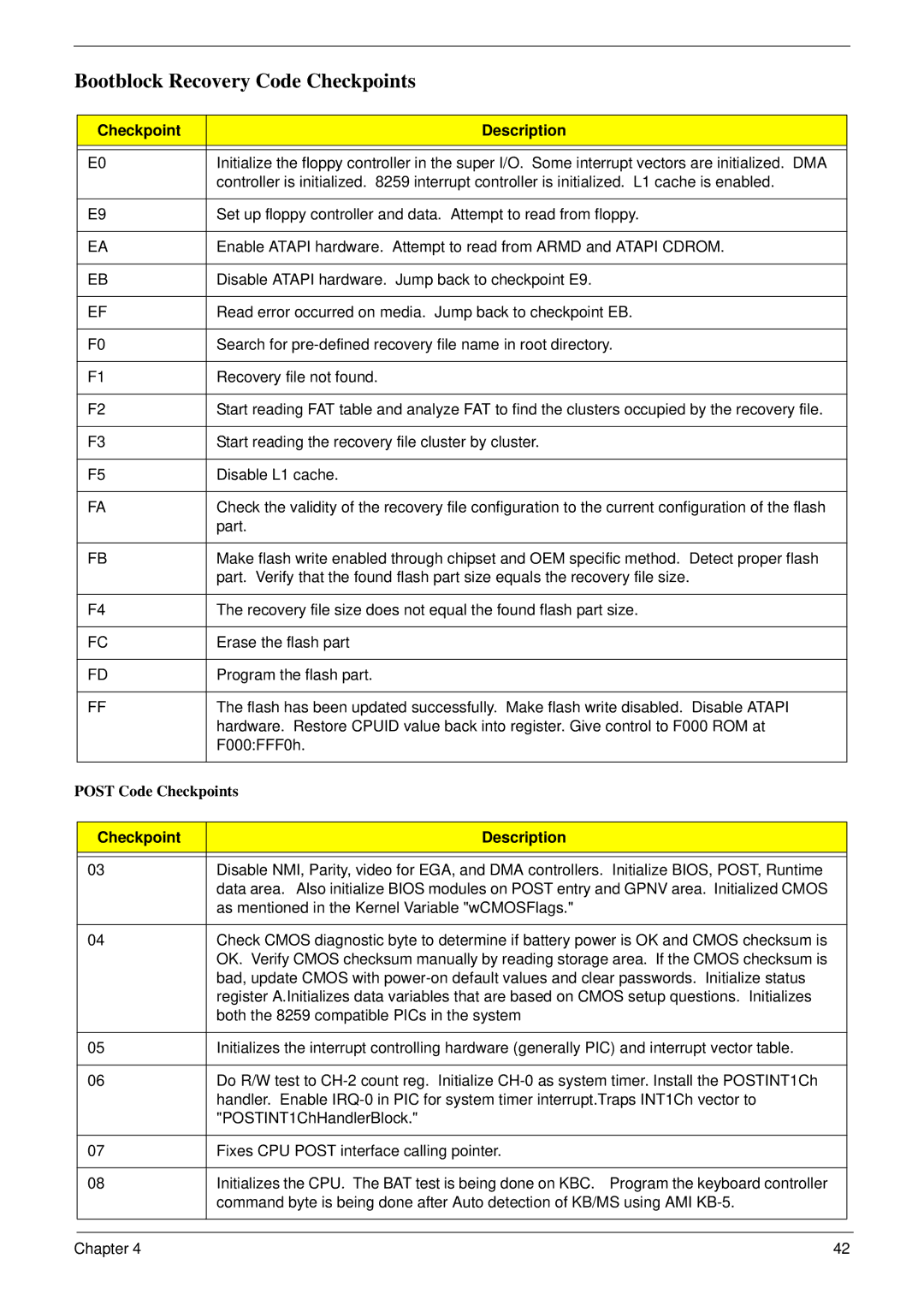

Bootblock Recovery Code Checkpoints

| Checkpoint | Description |

|

|

|

|

|

| E0 | Initialize the floppy controller in the super I/O. Some interrupt vectors are initialized. DMA |

|

|

| controller is initialized. 8259 interrupt controller is initialized. L1 cache is enabled. |

|

|

|

|

|

| E9 | Set up floppy controller and data. Attempt to read from floppy. |

|

|

|

|

|

| EA | Enable ATAPI hardware. Attempt to read from ARMD and ATAPI CDROM. |

|

|

|

|

|

| EB | Disable ATAPI hardware. Jump back to checkpoint E9. |

|

|

|

|

|

| EF | Read error occurred on media. Jump back to checkpoint EB. |

|

|

|

|

|

| F0 | Search for |

|

|

|

|

|

| F1 | Recovery file not found. |

|

|

|

|

|

| F2 | Start reading FAT table and analyze FAT to find the clusters occupied by the recovery file. |

|

|

|

|

|

| F3 | Start reading the recovery file cluster by cluster. |

|

|

|

|

|

| F5 | Disable L1 cache. |

|

|

|

|

|

| FA | Check the validity of the recovery file configuration to the current configuration of the flash |

|

|

| part. |

|

|

|

|

|

| FB | Make flash write enabled through chipset and OEM specific method. Detect proper flash |

|

|

| part. Verify that the found flash part size equals the recovery file size. |

|

|

|

|

|

| F4 | The recovery file size does not equal the found flash part size. |

|

|

|

|

|

| FC | Erase the flash part |

|

|

|

|

|

| FD | Program the flash part. |

|

|

|

|

|

| FF | The flash has been updated successfully. Make flash write disabled. Disable ATAPI |

|

|

| hardware. Restore CPUID value back into register. Give control to F000 ROM at |

|

|

| F000:FFF0h. |

|

|

|

|

|

POST Code Checkpoints |

| ||

|

|

|

|

| Checkpoint | Description |

|

|

|

|

|

| 03 | Disable NMI, Parity, video for EGA, and DMA controllers. Initialize BIOS, POST, Runtime |

|

|

| data area. Also initialize BIOS modules on POST entry and GPNV area. Initialized CMOS |

|

|

| as mentioned in the Kernel Variable "wCMOSFlags." |

|

|

|

|

|

| 04 | Check CMOS diagnostic byte to determine if battery power is OK and CMOS checksum is |

|

|

| OK. Verify CMOS checksum manually by reading storage area. If the CMOS checksum is |

|

|

| bad, update CMOS with |

|

|

| register A.Initializes data variables that are based on CMOS setup questions. Initializes |

|

|

| both the 8259 compatible PICs in the system |

|

|

|

|

|

| 05 | Initializes the interrupt controlling hardware (generally PIC) and interrupt vector table. |

|

|

|

|

|

| 06 | Do R/W test to |

|

|

| handler. Enable |

|

|

| "POSTINT1ChHandlerBlock." |

|

|

|

|

|

| 07 | Fixes CPU POST interface calling pointer. |

|

|

|

|

|

| 08 | Initializes the CPU. The BAT test is being done on KBC. Program the keyboard controller |

|

|

| command byte is being done after Auto detection of KB/MS using AMI |

|

|

|

|

|

|

|

|

|

Chapter 4 | 42 |