Post Codes

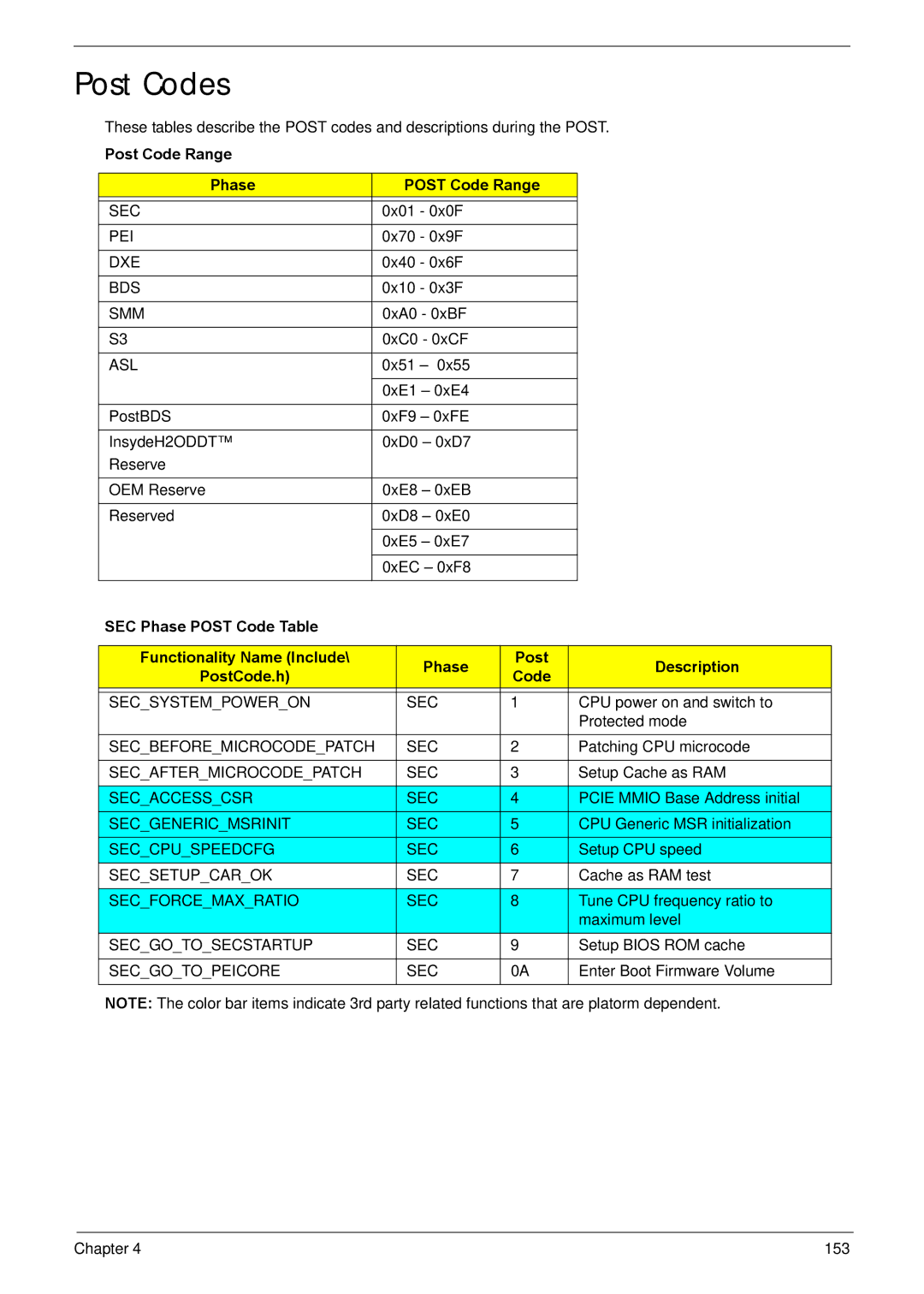

These tables describe the POST codes and descriptions during the POST.

Post Code Range

Phase | POST Code Range | |

|

|

|

SEC | 0x01 | - 0x0F |

|

|

|

PEI | 0x70 | - 0x9F |

|

|

|

DXE | 0x40 | - 0x6F |

|

|

|

BDS | 0x10 | - 0x3F |

|

| |

SMM | 0xA0 - 0xBF | |

|

| |

S3 | 0xC0 - 0xCF | |

|

|

|

ASL | 0x51 | – 0x55 |

|

| |

| 0xE1 – 0xE4 | |

|

| |

PostBDS | 0xF9 – 0xFE | |

|

| |

InsydeH2ODDT™ | 0xD0 – 0xD7 | |

Reserve |

|

|

|

| |

OEM Reserve | 0xE8 – 0xEB | |

|

| |

Reserved | 0xD8 – 0xE0 | |

|

| |

| 0xE5 – 0xE7 | |

|

| |

| 0xEC – 0xF8 | |

|

|

|

SEC Phase POST Code Table

Functionality Name (Include\ | Phase | Post | Description | |

PostCode.h) | Code | |||

|

| |||

|

|

|

| |

SEC_SYSTEM_POWER_ON | SEC | 1 | CPU power on and switch to | |

|

|

| Protected mode | |

|

|

|

| |

SEC_BEFORE_MICROCODE_PATCH | SEC | 2 | Patching CPU microcode | |

|

|

|

| |

SEC_AFTER_MICROCODE_PATCH | SEC | 3 | Setup Cache as RAM | |

|

|

|

| |

SEC_ACCESS_CSR | SEC | 4 | PCIE MMIO Base Address initial | |

SEC_GENERIC_MSRINIT | SEC | 5 | CPU Generic MSR initialization | |

SEC_CPU_SPEEDCFG | SEC | 6 | Setup CPU speed | |

SEC_SETUP_CAR_OK | SEC | 7 | Cache as RAM test | |

|

|

|

| |

SEC_FORCE_MAX_RATIO | SEC | 8 | Tune CPU frequency ratio to | |

|

|

| maximum level | |

SEC_GO_TO_SECSTARTUP | SEC | 9 | Setup BIOS ROM cache | |

|

|

|

| |

SEC_GO_TO_PEICORE | SEC | 0A | Enter Boot Firmware Volume | |

|

|

|

|

NOTE: The color bar items indicate 3rd party related functions that are platorm dependent.

Chapter 4 | 153 |