Your ePlatform Partner

User’s Manual for Advantech

|

|

| memory | block. | About | detail |

| ||||

|

|

| description, | please |

| reference |

| ||||

|

|

|

|

| Memory and |

| |||||

|

|

| Interrupt Map”. |

|

|

|

|

|

| ||

|

|

| Static chip selects. Chip selects to |

| |||||||

|

|

| static memory devices such as ROM |

| |||||||

|

|

| and | Flash. |

|

| Individually |

| |||

|

|

| programmable | in | the | memory |

| ||||

|

|

| configuration registers. nBUF_CS5 |

| |||||||

|

|

| can be used with variable latency I/O | Pull high | |||||||

|

|

| devices. |

|

|

|

|

|

| ||

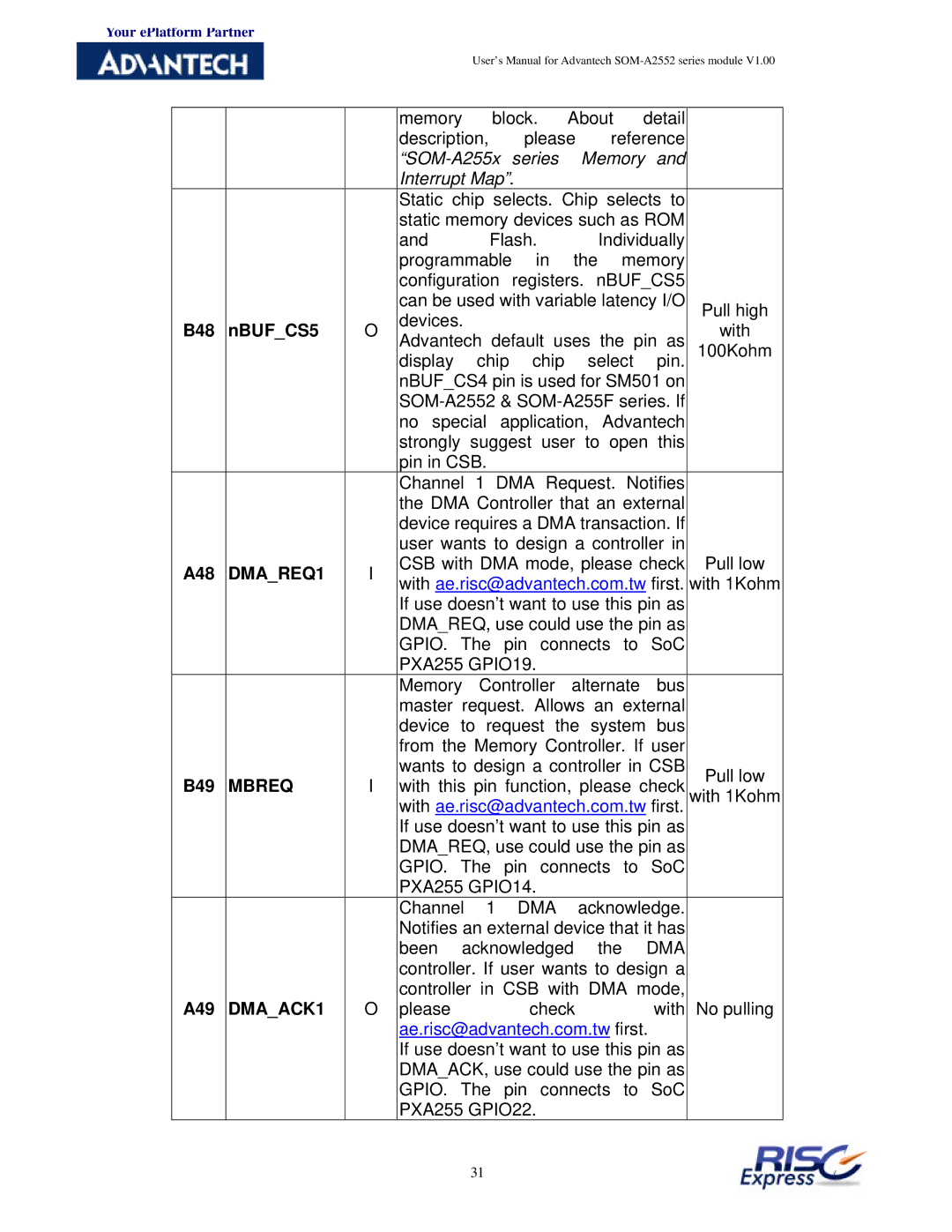

B48 | nBUF_CS5 | O |

|

|

|

|

|

| with | ||

Advantech default uses the pin as | |||||||||||

|

|

| 100Kohm | ||||||||

|

|

| display | chip | chip |

| select | pin. | |||

|

|

| nBUF_CS4 pin is used for SM501 on |

| |||||||

|

|

|

| ||||||||

|

|

| no special application, | Advantech |

| ||||||

|

|

| strongly suggest user to open this |

| |||||||

|

|

| pin in CSB. |

|

|

|

|

|

| ||

|

|

| Channel 1 DMA Request. Notifies |

| |||||||

|

|

| the DMA Controller that an external |

| |||||||

|

|

| device requires a DMA transaction. If |

| |||||||

|

|

| user wants to design a controller in |

| |||||||

A48 | DMA_REQ1 | I | CSB with DMA mode, please check | Pull low | |||||||

with ae.risc@advantech.com.tw first. | with 1Kohm | ||||||||||

|

|

| |||||||||

|

|

| If use doesn’t want to use this pin as |

| |||||||

|

|

| DMA_REQ, use could use the pin as |

| |||||||

|

|

| GPIO. The pin connects to SoC |

| |||||||

|

|

| PXA255 GPIO19. |

|

|

|

|

| |||

|

|

| Memory | Controller | alternate | bus |

| ||||

|

|

| master request. Allows an external |

| |||||||

|

|

| device to request the system bus |

| |||||||

|

|

| from the Memory Controller. If user |

| |||||||

|

|

| wants to design a controller in CSB | Pull low | |||||||

B49 | MBREQ | I | with this pin function, please check | ||||||||

with 1Kohm | |||||||||||

|

|

| with ae.risc@advantech.com.tw first. |

| |||||||

|

|

| If use doesn’t want to use this pin as |

| |||||||

|

|

| DMA_REQ, use could use the pin as |

| |||||||

|

|

| GPIO. The pin connects to SoC |

| |||||||

|

|

| PXA255 GPIO14. |

|

|

|

|

| |||

|

|

| Channel | 1 | DMA |

| acknowledge. |

| |||

|

|

| Notifies an external device that it has |

| |||||||

|

|

| been acknowledged |

| the | DMA |

| ||||

|

|

| controller. If user wants to design a |

| |||||||

|

|

| controller in CSB with DMA mode, |

| |||||||

A49 | DMA_ACK1 | O | please |

| check |

|

| with | No pulling | ||

|

|

| ae.risc@advantech.com.tw first. |

| |||||||

|

|

| If use doesn’t want to use this pin as |

| |||||||

|

|

| DMA_ACK, use could use the pin as |

| |||||||

|

|

| GPIO. The pin connects to SoC |

| |||||||

|

|

| PXA255 GPIO22. |

|

|

|

|

| |||

31