Your ePlatform Partner

User’s Manual for Advantech

|

|

| of the next one. The state of |

|

|

|

| VPHSYNC |

|

|

|

| determines whether the current |

|

|

|

| capture |

|

|

|

| field is ODD (VPHREF is High on |

|

|

|

| the |

|

|

|

| active edge of VPVSYNC) or |

|

|

|

| EVEN |

|

|

|

| (VPHREF is Low on the active |

|

|

|

| edge of |

|

|

|

| VPVSYNC). |

|

A50 |

|

| Pixel Clock. VPCLK is the | No pulling |

| VPCLK | I | reference clock for data on the |

|

|

|

| ZV[31:0] video pixel bus. |

|

2.2 function description

2.2.1 System Bus

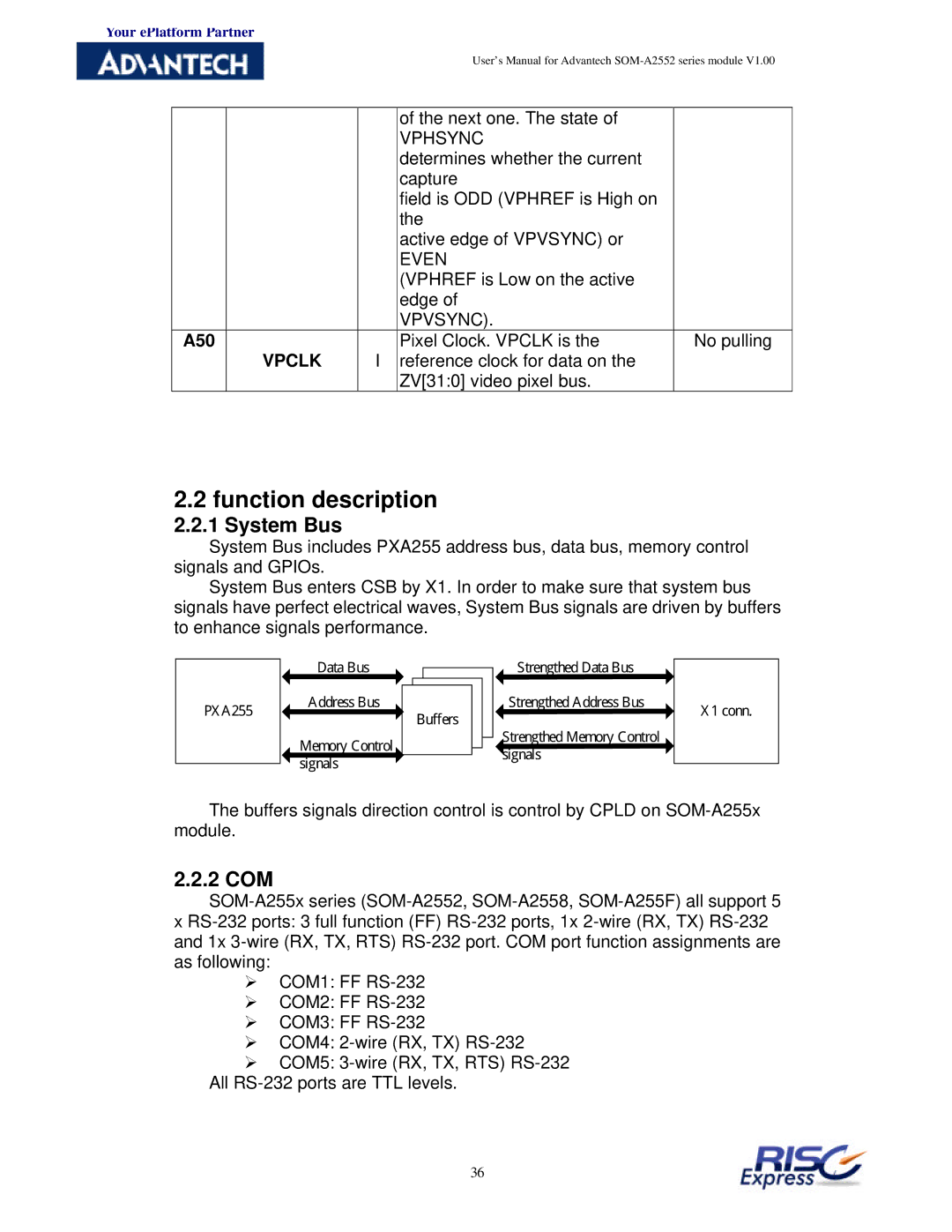

System Bus includes PXA255 address bus, data bus, memory control signals and GPIOs.

System Bus enters CSB by X1. In order to make sure that system bus signals have perfect electrical waves, System Bus signals are driven by buffers to enhance signals performance.

芇爧

… 蚺

㷇 鑃

蚰

鑃

蛈 鑃

蛅 蚺

蚽

覂

The buffers signals direction control is control by CPLD on

2.2.2 COM

x

ØCOM1: FF

ØCOM2: FF

ØCOM3: FF

ØCOM4:

ØCOM5:

All

36