Your ePlatform Partner

User’s Manual for Advantech

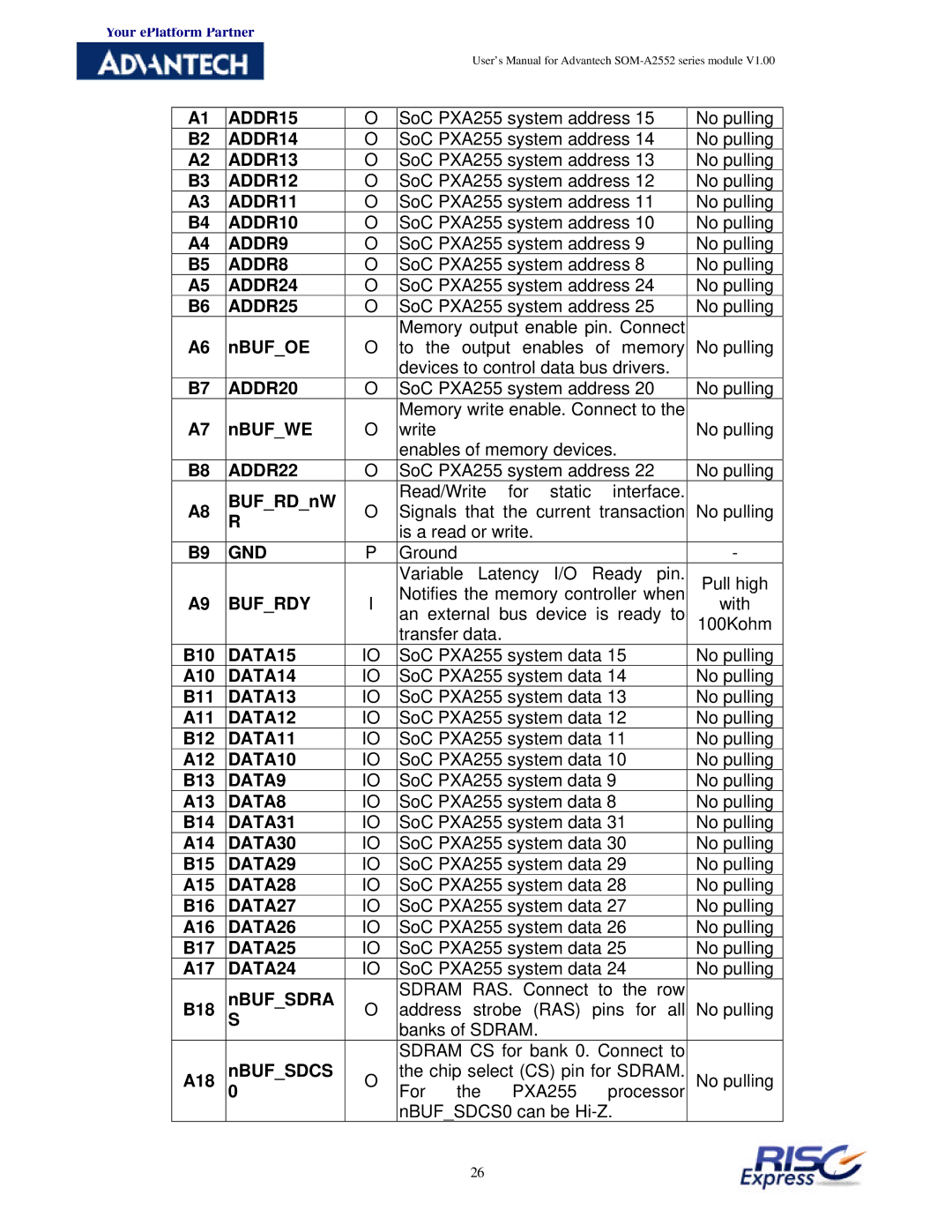

A1 | ADDR15 | O | SoC PXA255 system address 15 | No pulling | ||||

B2 | ADDR14 | O | SoC PXA255 system address 14 | No pulling | ||||

A2 | ADDR13 | O | SoC PXA255 system address 13 | No pulling | ||||

B3 | ADDR12 | O | SoC PXA255 system address 12 | No pulling | ||||

A3 | ADDR11 | O | SoC PXA255 system address 11 | No pulling | ||||

B4 | ADDR10 | O | SoC PXA255 system address 10 | No pulling | ||||

A4 | ADDR9 | O | SoC PXA255 system address 9 | No pulling | ||||

B5 | ADDR8 | O | SoC PXA255 system address 8 | No pulling | ||||

A5 | ADDR24 | O | SoC PXA255 system address 24 | No pulling | ||||

B6 | ADDR25 | O | SoC PXA255 system address 25 | No pulling | ||||

|

|

| Memory output enable pin. Connect |

| ||||

A6 | nBUF_OE | O | to the output enables of memory | No pulling | ||||

|

|

| devices to control data bus drivers. |

| ||||

B7 | ADDR20 | O | SoC PXA255 system address 20 | No pulling | ||||

|

|

| Memory write enable. Connect to the |

| ||||

A7 | nBUF_WE | O | write |

|

|

| No pulling | |

|

|

| enables of memory devices. |

| ||||

B8 | ADDR22 | O | SoC PXA255 system address 22 | No pulling | ||||

| BUF_RD_nW |

| Read/Write | for | static | interface. |

| |

A8 | O | Signals that the current transaction | No pulling | |||||

R | ||||||||

|

| is a read or write. |

|

|

| |||

|

|

|

|

|

| |||

B9 | GND | P | Ground |

|

|

| - | |

|

|

| Variable Latency | I/O | Ready pin. | Pull high | ||

|

|

| Notifies the memory controller when | |||||

A9 | BUF_RDY | I | with | |||||

an external bus device is ready to | ||||||||

|

|

| 100Kohm | |||||

|

|

| transfer data. |

|

|

|

| |

B10 | DATA15 | IO | SoC PXA255 system data 15 | No pulling | ||||

A10 | DATA14 | IO | SoC PXA255 system data 14 | No pulling | ||||

B11 | DATA13 | IO | SoC PXA255 system data 13 | No pulling | ||||

A11 | DATA12 | IO | SoC PXA255 system data 12 | No pulling | ||||

B12 | DATA11 | IO | SoC PXA255 system data 11 | No pulling | ||||

A12 | DATA10 | IO | SoC PXA255 system data 10 | No pulling | ||||

B13 | DATA9 | IO | SoC PXA255 system data 9 | No pulling | ||||

A13 | DATA8 | IO | SoC PXA255 system data 8 | No pulling | ||||

B14 | DATA31 | IO | SoC PXA255 system data 31 | No pulling | ||||

A14 | DATA30 | IO | SoC PXA255 system data 30 | No pulling | ||||

B15 | DATA29 | IO | SoC PXA255 system data 29 | No pulling | ||||

A15 | DATA28 | IO | SoC PXA255 system data 28 | No pulling | ||||

B16 | DATA27 | IO | SoC PXA255 system data 27 | No pulling | ||||

A16 | DATA26 | IO | SoC PXA255 system data 26 | No pulling | ||||

B17 | DATA25 | IO | SoC PXA255 system data 25 | No pulling | ||||

A17 | DATA24 | IO | SoC PXA255 system data 24 | No pulling | ||||

| nBUF_SDRA |

| SDRAM RAS. Connect to the row |

| ||||

B18 | O | address strobe (RAS) pins for all | No pulling | |||||

S | ||||||||

|

|

| banks of SDRAM. |

|

|

| ||

|

|

| SDRAM CS for bank 0. Connect to |

| ||||

A18 | nBUF_SDCS | O | the chip select (CS) pin for SDRAM. | No pulling | ||||

| 0 |

| For the | PXA255 | processor |

| ||

|

|

| nBUF_SDCS0 can be |

| ||||

26