30.6 SteadyClock

The SteadyClock technology of the HDSP MADI guarantees an excellent performance in all clock modes. Its highly efficient jitter suppression refreshes and cleans up any clock signal, and provides it as reference clock at the word clock output.

Usually a clock section consists of an analog PLL for external synchronization and several quartz oscillators for internal synchronisation. SteadyClock requires only one quartz, using a frequency not equalling digital audio. Latest circuit designs like

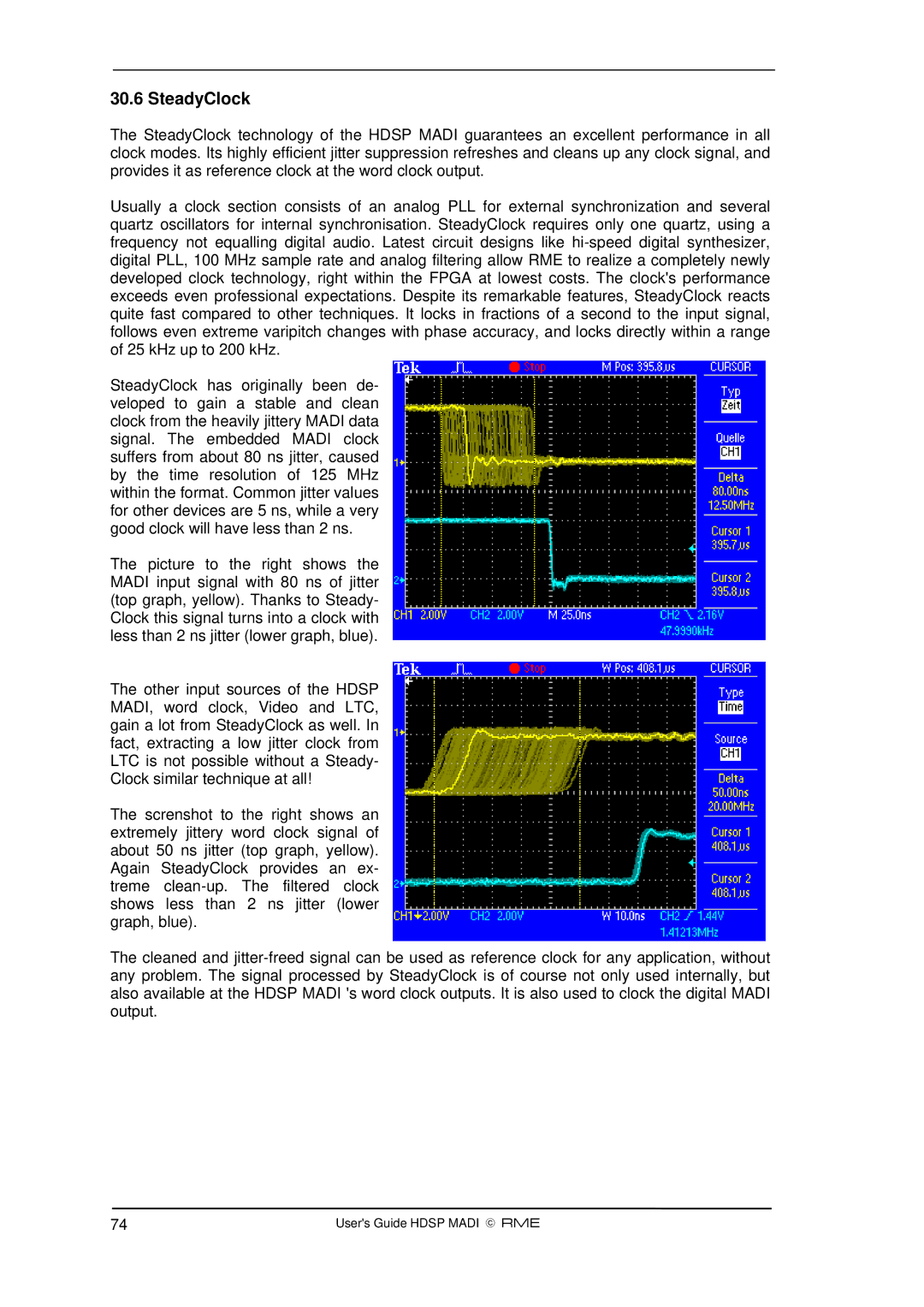

SteadyClock has originally been de- veloped to gain a stable and clean clock from the heavily jittery MADI data signal. The embedded MADI clock suffers from about 80 ns jitter, caused by the time resolution of 125 MHz within the format. Common jitter values for other devices are 5 ns, while a very good clock will have less than 2 ns.

The picture to the right shows the MADI input signal with 80 ns of jitter (top graph, yellow). Thanks to Steady- Clock this signal turns into a clock with less than 2 ns jitter (lower graph, blue).

The other input sources of the HDSP MADI, word clock, Video and LTC, gain a lot from SteadyClock as well. In fact, extracting a low jitter clock from LTC is not possible without a Steady- Clock similar technique at all!

The screnshot to the right shows an extremely jittery word clock signal of about 50 ns jitter (top graph, yellow). Again SteadyClock provides an ex- treme

The cleaned and

74 | User's Guide HDSP MADI © RME |