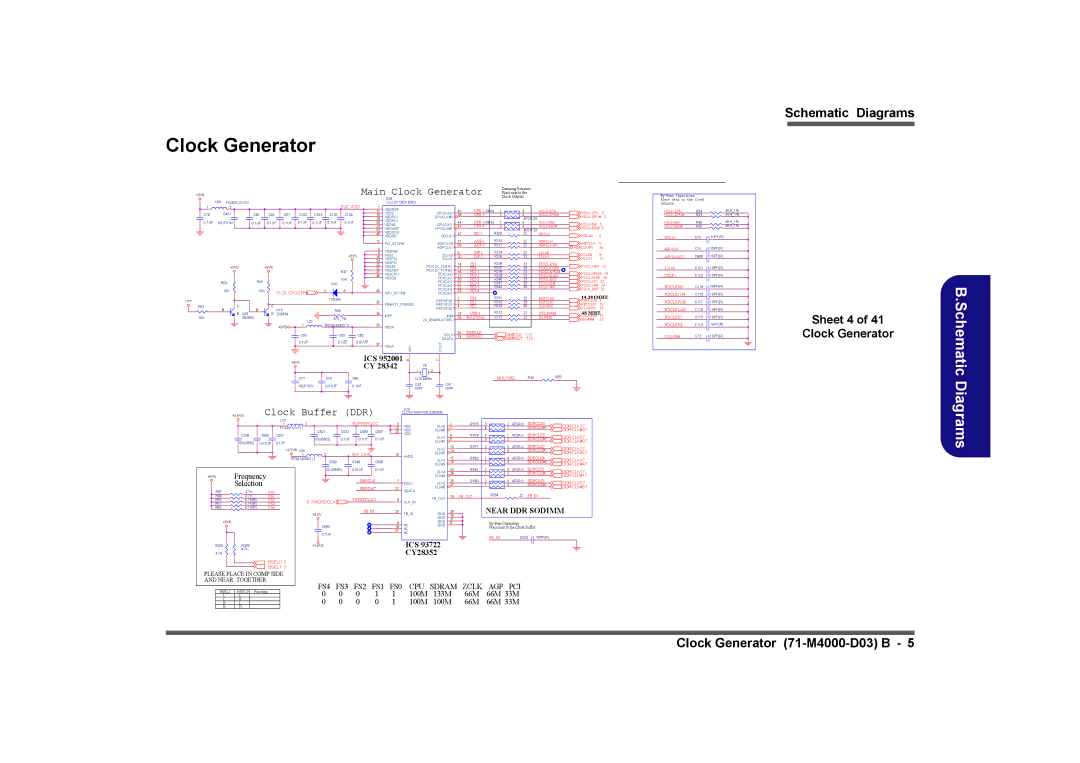

Clock Generator

Schematic Diagrams

+3VS |

|

|

|

|

|

|

|

| MainU28Clock Generator | Clock Outputs |

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Damping Resistors |

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Place near to the |

|

|

|

| |

| L84 FCM2012V121 |

|

|

|

|

|

| CLK_VCC3 |

| CLOCK GEN (650) |

|

|

|

|

|

|

|

|

| ||

1 | 2 |

|

|

|

|

|

| 1 | VDDREF |

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

| 11 |

|

| 40 | 1 | 4 | 3 | |||||

C76 | C401 | C85 | C84 | C81 | C102 | C103 | C105 | C104 | 13 | VDDZ |

| CPUCLK0 | 39 |

| 2 | 3 | |||||

|

|

|

|

|

|

|

|

|

| 19 | VDDPCI |

| CPUCLK#0 |

|

|

|

| 3 | |||

0.1UF | 10UF/10V | 0.1UF | 0.1UF 0.1UF | 0.1UF | 0.1UF | 0.1UF | 0.1UF | 28 | VDDPCI |

|

| 44 | 1 | 4 | 5 |

| |||||

VDD48 |

| CPUCLK1 |

| ||||||||||||||||||

|

|

|

|

|

|

|

|

|

| 29 |

| 43 | 2 | 3 |

| ||||||

|

|

|

|

|

|

|

|

|

| 42 | VDDAGP |

| CPUCLK#1 |

|

|

|

| 5 | |||

|

|

|

|

|

|

|

|

|

| 48 | VDDCPU |

| SDCLK | 47 | R309 | 22 | SDCLK | SDCLK | 6 |

| |

|

|

|

|

|

|

|

|

|

|

| VDDSD |

|

| R310 |

|

|

| ||||

|

|

|

|

|

|

|

|

|

| 12 | PCI_STOP# |

| AGPCLK0 | 31 | 22 | AGPCLK | AGPCLK | 5 |

| ||

|

|

|

|

|

|

|

|

|

|

|

| 30 | R311 | 22 | AGPCLKATI |

| |||||

|

|

|

|

|

|

|

|

|

| 5 | VSSREF |

| AGPCLK1 |

| R334 | 22 |

| AGPCLKATI | 30 |

| |

|

|

|

|

|

|

|

|

|

| 8 |

|

| 9 | ZCLK0 | ZCLK0 | 9 |

| ||||

|

|

|

|

|

|

|

|

| +3VS | 18 | VSSZ |

| ZCLK0 | 10 | R335 | 22 | ZCLK1 |

| |||

|

|

|

|

|

|

|

|

|

| 24 | VSSPCI |

| ZCLK1 |

|

|

|

|

| ZCLK1 | 13 |

|

|

|

|

|

|

|

|

|

|

| VSSPCI |

|

| 14 | FS3 | R336 | 33 | PCICLK961 |

|

|

| |

|

|

|

|

|

|

|

|

|

| 25 |

|

| PCICLK961 | 13 | |||||||

| +3VS |

| +3VS |

|

|

|

| R37 |

| 32 | VSS48 |

| PCICLK_F0/FS3 | 15 | FS4 | R337 | 33 | PCICLK1394 | |||

|

|

|

|

|

|

|

|

| 41 | VSSAGP |

| PCICLK_F1/FS4 | 16 | R338 | 33 | PCICLKPCM | T |

|

| ||

|

|

|

|

|

|

|

|

|

| 46 | VSSCPU |

| PCICLK0 | 17 | R339 | 33 | PCICLKLAN | PCICLKPCM | 19 | ||

|

|

|

|

|

|

|

| 10K |

|

| VSSSD |

| PCICLK1 | 20 | R340 | 33 | PCICLKIO | PCICLKLAN | 25 | ||

| R59 | R43 |

|

|

|

| D10 |

|

|

|

|

| PCICLK2 | 21 | R341 | 33 | PCICLKH8 | PCICLKIO | 22 | ||

|

|

|

|

|

|

|

|

|

|

|

|

| PCICLK3 | 22 | R342 | 33 | PCLK_80P | PCICLKH8 | 24 | ||

| 10K | 10K | 15,29 CPUSTP# |

| C | A |

| 45 | CPU_STOP# | PCICLK4 | 23 | T |

|

| PCLK_80P | 20 | |||||

|

|

|

|

|

|

|

|

| PCICLK5 |

|

|

|

| 14.381MHZ | |||||||

VTT |

|

|

|

|

|

| 1SS355 |

| 33 |

|

| REF0/FS0 | 2 | FS0 | R331 | 33 | REFCLK0 | ||||

|

|

|

|

|

|

|

|

|

|

| 3 | FS1 | R332 | 33 | REFCLK1 | REFCLK0 | 9 |

| |||

R62 | C |

| C |

|

|

|

|

|

|

| PD#/VTT_PWRGD | REF1/FS1 | 4 | FS2 | R333 | 33 | CLKAPIC | REFCLK1 | 15 |

| |

| B | B |

| Q19 |

|

| R45 |

|

|

|

| REF2/FS2 |

|

|

|

|

| CLKAPIC | 15 |

| |

| E |

|

|

| 38 |

|

|

| 27 | R312 | 22 | UCLK48M | 48 MHZ |

| |||||||

| E Q20 |

| 2N3904 |

|

|

|

|

| IREF |

| 48M |

| |||||||||

10K | 2N3904 |

|

|

|

| 475_1% |

|

|

| 26 | MULTISEL | R313 | 22 | SIO48M | UCLK48M | 16 |

| ||||

|

| L21 |

|

|

|

| 24_48M/MULTISEL | SIO48M | 22 |

| |||||||||||

|

|

|

| +3VS | 1 |

| 2FCM1608K121 | 36 | VDDA |

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

| C90 |

|

| C83 | C82 |

|

|

| SCLK | 35 | SMBCLK | SMBCLK | 7,15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 34 | SMBDAT |

|

|

|

| ||||||

|

|

|

|

| 0.1UF |

|

| 0.1UF | 0.01UF |

|

|

| SDATA |

|

| SMBDAT | 7,15 |

|

|

|

|

|

|

|

|

|

|

| 37 | VSSA | XIN | XOUT |

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

| +3VS |

|

|

| ICS 952001 | 6 | 7 |

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

| CY 28342 | Y5 |

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

| 1 | 2 |

|

|

|

|

|

|

|

|

|

|

|

|

| C77 |

| C78 |

| C86 |

|

| 14.318MHz |

|

| MULTISEL | R44 | 0(R) |

|

|

| |

|

|

|

|

| 10UF/10V | 0.01UF |

| 0.1UF |

|

| C92 | C91 |

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

| 10PF | 10PF |

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| +2.5VS |

| Clock Buffer (DDR) |

|

| U29 |

|

|

|

|

|

|

|

|

| ||||||

CLOCK BUFFER (DDR48)

|

|

| L33 |

|

| BUFFERVCC |

|

|

|

|

|

|

|

| DDRCLK3 |

| ||

|

|

| 1 | 2 |

| 3 | VDD | CLK0 | 2 | RP75 | 3 | 2 | DDRCLK37 | |||||

|

|

| FCM2012V121 |

|

|

|

| 12 | 1 |

| 4 | 1 |

| DDRCLK#3 | ||||

|

|

|

|

|

|

| VDD | CLK#0 |

|

| DDRCLK#37 | |||||||

|

|

|

| C523 | C532 | C550 | C557 | 23 |

|

|

|

|

|

|

| |||

| C208 | C565 | C207 | VDD |

| 4 | RP76 | 4 | 1 | DDRCLK0 |

| |||||||

|

|

|

|

|

| CLK1 | DDRCLK07 | |||||||||||

|

|

|

| 10U(0805) | 0.1UF | 0.1UF | 0.1UF |

|

| 5 |

| 3 | 2 |

| DDRCLK#0 | |||

| 10U(0805) | 0.01UF | 0.1UF |

|

| CLK#1 |

|

| DDRCLK#07 | |||||||||

|

|

|

|

|

|

|

|

|

|

|

| DDRCLK2 | ||||||

|

|

|

|

|

|

|

| 13 | RP77 | 2 | 3 |

| ||||||

|

|

| +2.5VS L94 |

|

|

|

|

|

| CLK2 | DDRCLK27 | |||||||

|

|

|

|

|

|

|

|

| 14 |

| 1 | 4 |

| DDRCLK#2 | ||||

|

|

|

|

|

|

|

|

| CLK#2 |

|

| DDRCLK#27 | ||||||

|

|

| 1 | 2 |

| BUF_2.5VS |

| 10 | AVDD |

|

|

|

|

| DDRCLK4 | |||

|

|

| FCM1608K121 |

|

|

|

| CLK3 | 17 | RP62 | 1 | 4 | DDRCLK47 | |||||

|

|

|

|

|

|

|

| |||||||||||

|

|

|

| C560 |

| C549 | C556 |

|

| 16 |

| 2 | 3 |

| DDRCLK#4 | |||

|

|

|

|

|

|

| CLK#3 |

|

| DDRCLK#47 | ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| DDRCLK1 | |||

|

|

|

| 10U(0805) | 0.01UF | 0.1UF |

|

| CLK4 | 24 | RP61 | 2 | 3 | DDRCLK17 | ||||

| Frequency |

|

|

|

|

|

|

| 25 |

| 1 | 4 |

| DDRCLK#1 | ||||

+3VS |

|

|

|

|

|

|

| CLK#4 |

|

| DDRCLK#17 | |||||||

|

|

| SMBCLK | 7 |

| 26 | RP60 | 2 | 3 | DDRCLK5 | ||||||||

| Selection |

|

|

| SCLK | CLK#5 | DDRCLK#57 | |||||||||||

|

|

|

|

|

|

| 27 |

| 1 | 4 |

| DDRCLK#5 | ||||||

|

|

|

|

|

| SMBDAT |

| CLK5 |

|

|

|

|

|

|

| DDRCLK57 | ||

R67 | 4.7K | FS0 |

|

|

| 22 | SDATA |

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

| R384 |

| 22 | FB_IN |

| |||||

R66 | 4.7K | FS1 |

|

|

| FWDSDCLKO |

|

| FB_OUT | 19 | FB_OUT |

|

| |||||

R65 | 4.7K(R) | FS2 |

| 6 FWDSDCLKO |

| 8 | CLK_IN |

|

|

|

|

|

|

|

| |||

R61 | 4.7K(R) | FS3 |

|

|

|

|

|

|

|

| NEAR DDR SODIMM | |||||||

R60 | 4.7K(R) | FS4 |

|

|

| FB_IN |

| 20 |

|

| 28 |

| ||||||

|

|

|

| +2.5V |

|

| FB_IN | GND |

| |||||||||

|

|

|

|

|

|

|

|

| GND | 15 |

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

| 11 |

|

|

|

|

|

|

| |

+3VS |

|

|

|

|

|

|

| 9 |

| GND |

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

| 6 |

|

|

|

| ||||||

|

|

|

| C684 |

| T |

| 18 | NC | GND |

|

| Place near to the Clock Buffer |

|

| |||

|

|

|

|

| T |

| NC |

|

|

|

|

| ||||||

|

|

|

|

|

|

| 21 |

|

|

|

|

|

|

|

|

| ||

|

|

|

| 0.1UF |

| T |

| NC |

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

| FB_IN |

| C533 | 10PF(R) |

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

| ICS 93722 |

|

|

|

| |||||

R283 | R296 |

|

| +1.8VS |

|

|

|

|

|

|

|

|

|

|

|

| ||

4.7K | 4.7K |

|

|

|

|

|

|

| CY28352 |

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

BSEL0 3

BSEL1 3

PLEASE PLACE IN COMP SIDE

AND NEAR TOGETHER

|

|

|

|

| FS4 | FS3 | FS2 | FS1 | FS0 | CPU SDRAM ZCLK AGP PCI | ||||

|

|

|

|

| ||||||||||

| L | L |

| 0 | 0 | 0 | 1 | 1 | 100M | 133M | 66M | 66M | 33M | |

| BSEL1 | BSEL0 | Function |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 0 | 0 | 0 | 0 | 1 | 100M | 100M | 66M | 66M | 33M | |

| L | H |

| |||||||||||

| H | L |

| |||||||||||

| H | H |

|

|

|

|

|

|

|

|

|

|

|

|

SDCLK | C75 |

|

AGPCLK | C74 |

|

AGPCLKATI | C688 | |

|

|

|

ZCLK0 | C121 | |

|

|

|

ZCLK1 | C120 | |

|

|

|

PCICLK961 | C119 | |

|

|

|

PCICLK1394 | C118 | |

|

|

|

PCICLKPCM | C117 | |

|

|

|

PCICLKLAN | C116 | |

|

|

|

PCICLKIO | C115 | |

|

|

|

PCICLKH8 | C114 | |

UCLK48M | C73 |

|

49.9_1% |

49.9_1% |

49.9_1% |

49.9_1% |

10PF(R) |

10PF(R) |

10PF(R) |

10PF(R) |

10PF(R) |

10PF(R) |

10PF(R) |

10PF(R) |

10PF(R) |

10PF(R) |

10PF(R) |

10PF(R) |

Sheet 4 of 41

Clock Generator

B.Schematic Diagrams

Clock Generator