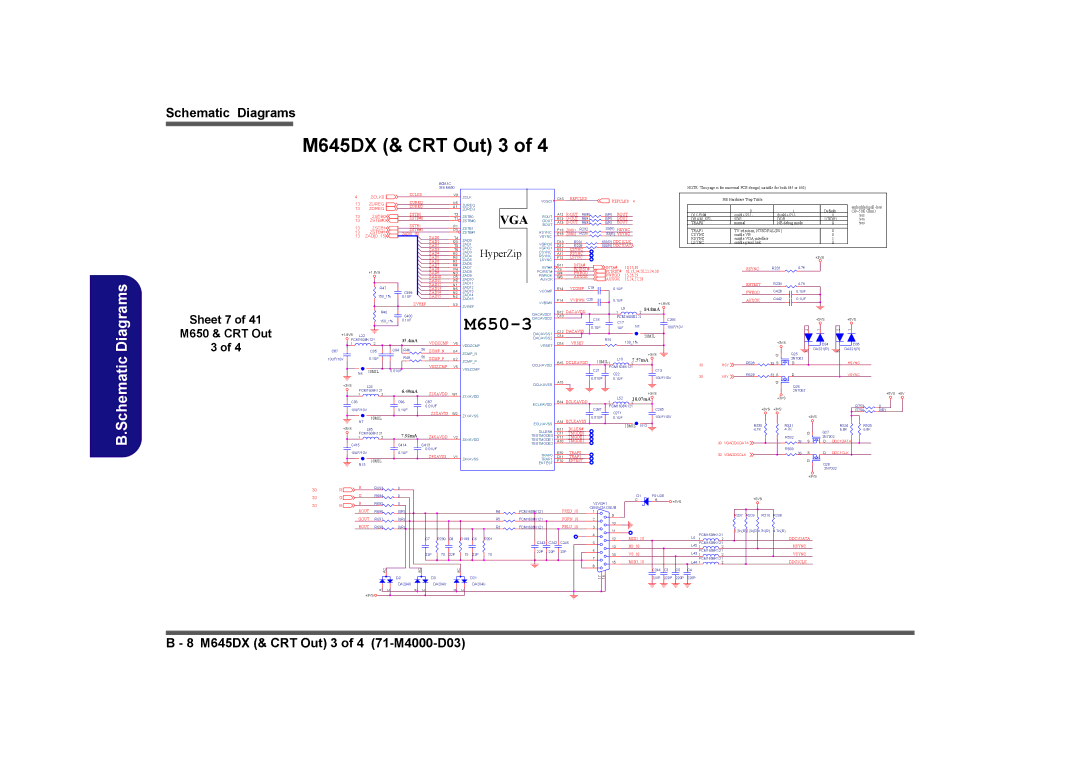

B.Schematic Diagrams

Schematic Diagrams

M645DX (& CRT Out) 3 of 4

BGA1C | NOTE: This page is for universal PCB design( suitable for both 645 or 650) |

SIS M650 |

|

| 4 |

| ZCLK0 |

|

| ZCLK0 |

|

| V3 | ZCLK |

|

|

|

|

| C15 | REFCLK0 |

|

|

|

|

|

|

|

|

|

| NB Hardware Trap Table |

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

| ZUREQ |

|

|

|

|

|

| VOSCI | REFCLK0 | 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||

|

| 13 | ZUREQ |

|

|

|

| U6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||

|

|

|

|

|

| ZUREQ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| embedded |

| |||||||||

|

| 13 | ZDREQ |

|

| ZDREQ |

|

| U1 | ZDREQ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

| ZSTB0 |

|

|

| VGA |

|

|

|

|

| ROUT |

|

|

|

|

|

|

|

| 0 |

|

| 1 |

| Default |

| (30~50K Ohm) |

|

| ||||||||||

|

| 13 |

| ZSTB0 |

|

|

|

| T3 | ZSTB0 | ROUT | A12 | R690 | 0(R) |

|

|

|

|

| DLLEN# | enable PLL |

| disable PLL |

|

| 0 |

| yes |

|

| ||||||||||||

|

|

|

|

| ZSTB#0 |

|

| T1 | B13 | R691 | 0(R) | GOUT |

|

|

|

|

| DRAM_SEL | SDR |

|

| DDR |

| 1(DDR) |

| yes |

|

| ||||||||||||||

|

| 13 |

| ZSTB#0 |

|

|

|

| ZSTB#0 | GOUT |

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||

|

|

|

|

|

|

|

|

|

| A13 | R692 | 0(R) | BOUT |

|

|

|

|

| TRAP0 | normal |

|

| NB debug mode |

|

| 0 |

| yes |

|

| ||||||||||||

|

|

|

|

|

|

| ZSTB1 |

|

| P1 |

|

| BOUT |

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||

|

| 13 |

| ZSTB1 |

|

|

|

| ZSTB1 |

|

| R232 | 33(R) HSYNC |

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||

|

|

|

|

| ZSTB#1 |

|

| P3 |

|

|

|

| F13 | Z0801 |

|

|

|

| TRAP1 | TV selection, NTSC/PAL(0/1) |

|

|

| 0 |

|

|

|

| ||||||||||||||

|

| 13 |

| ZSTB#1 |

|

| ZAD[0..15] |

|

|

|

| ZSTB#1 |

|

| HSYNC | E13 | Z0802 | R230 | 33(R) VSYNC |

|

|

|

| CSYNC | enable VB |

|

|

|

|

| 0 |

|

|

|

| |||||||

|

| 13 | ZAD[0..15] |

|

|

|

| ZAD0 | T4 | ZAD0 |

|

|

| VSYNC |

|

|

| 100(R) DDC1CLK |

|

|

|

| RSYNC | enable VGA interface |

|

|

|

| 1 |

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

| ZAD1 | R3 |

|

|

| VGPIO0 | D13 | R231 |

|

|

|

| LSYNC | enable panel link |

|

|

|

|

| 0 |

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

| ZAD2 | T5 | ZAD1 |

|

|

| D12 | R229 | 100(R) DDC1DATA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

| ZAD3 | T6 | ZAD2 |

| HyperZip | VGPIO1 | E12 | CSYNC | T |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| +3VS |

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

| ZAD5 | R6 | ZAD4 |

| RSYNC | F12 | LSYNC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

| ZAD4 | R2 | ZAD3 |

|

|

| CSYNC | A11 | RSYNC | T |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

| ZAD6 | R1 | ZAD5 |

|

|

| LSYNC |

| INTA# | T |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

| ZAD7 | R4 | ZAD6 |

|

|

| INT#A | B11 | INTA# | 10,13,30 |

|

|

|

|

|

|

| RSYNC |

|

| 4.7K |

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

| ZAD8 | P4 | ZAD7 |

|

|

| Y3 | PCIRST# |

|

|

|

|

|

|

|

| R233 |

|

|

|

|

|

| |||||||||||

|

|

| +1.8VS |

|

|

|

| ZAD9 | N3 | ZAD8 |

|

|

| PCIRST# | W4 | PWRGD | PCIRST# | 10,13,14,20,22,24,30 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

| ZAD9 |

|

|

| PWROK | PWRGD | 15,26,29 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||

|

|

|

|

|

|

|

|

| ZAD10 | P5 |

|

|

| W6 | AUXOK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

| ZAD10 |

|

| AUXOK | AUXOK | 15,24,27,28 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||

|

|

|

|

|

|

|

|

| ZAD11 | P6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

| ZAD12 | N1 | ZAD11 |

|

|

|

|

| VCOMP C19 |

|

|

|

|

|

|

|

|

|

| ENTEST |

| R234 | 4.7K |

|

|

|

|

|

| |||||

|

|

|

| R47 |

|

| C399 |

| ZAD13 | N6 | ZAD12 |

|

| VCOMP | E14 | 0.1UF |

|

|

|

|

|

|

|

|

| PWRGD |

| C428 | 0.1UF |

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

| ZAD14 | N2 | ZAD13 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

| 150_1% |

| 0.1UF |

| ZAD15 | N4 | ZAD14 |

|

|

|

|

| VVBWN C20 |

|

|

|

|

|

|

|

|

|

| AUXOK |

| C442 | 0.1UF |

|

|

|

|

|

| ||||||

|

|

|

|

|

|

| ZVREF |

| U3 | ZAD15 |

|

| VVBWN | F14 | 0.1UF |

|

|

| +1.8VS |

|

|

|

|

|

|

|

|

|

|

| ||||||||||||

|

|

|

|

|

|

|

| ZVREF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

| R46 |

|

|

|

|

|

|

|

|

|

| B12 | DACAVDD |

| 1 |

| 2 | 84.8mA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| L9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Sheet 7 of 41 |

|

|

|

|

|

| C400 |

|

|

|

|

|

|

|

| DACAVDD1 | C13 |

|

|

| C17 |

| N1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| DACAVDD2 |

|

| C18 | FCM1608K121 |

| C266 |

|

|

|

|

|

|

|

| +5VS |

| +5VS |

|

| ||||||||

|

|

|

| 150_1% |

| 0.1UF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

M650 & CRT Out |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| C12 | DACAVSS | 0.1UF | 1UF |

|

|

|

| 10UF/10V |

|

|

|

|

|

|

| 2 | 1 | 2 | 1 |

|

|

| ||

+1.8VS | L22 |

|

|

|

|

|

|

|

|

|

|

|

|

| DACAVSS1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

| C14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

FCM1608K121 |

|

| 35.4mA |

| VDDZCMP | V5 | D14 | VRSET | R16 |

| 130_1% |

| 20MIL |

|

|

|

|

|

|

| +3VS |

| D34 |

|

| D35 |

|

| ||||||||||||||

3 of 4 | 1 |

|

| 2 |

|

|

|

| VDDZCMP |

|

| VRSET |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||

|

|

|

| C94 | R48 | 56 | ZCMP_N |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| DA221(R) |

| DA221(R) |

|

| ||||||||

C87 |

|

| C95 | U4 | ZCMP_N |

|

|

|

|

|

|

|

|

|

|

|

| +3VS |

|

|

|

|

|

|

| G | Q25 | 3 | 3 |

|

| |||||||||||

| 10UF/10V |

| 0.1UF |

|

| R49 | 56 | ZCMP_P | U2 | ZCMP_P |

|

|

|

|

| DCLKAVDD | 10MIL1 | L10 |

| 27.57mA |

|

|

|

|

|

|

| 33 S | 2N7002 |

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

| VSSZCMP | V6 |

|

| DCLKAVDD | B15 |

|

|

|

|

| 30 | HSY | R528 |

| D |

|

|

| HSYNC |

|

| ||||||||||||

|

|

|

|

|

|

|

|

| VSSZCMP |

|

|

|

|

| FCM1608K121 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||

|

| N6 | 20MIL | 0.01UF |

|

|

|

|

|

|

|

|

|

|

| C21 |

|

|

|

| C13 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| C22 |

|

|

|

|

|

| 30 | VSY | R529 |

| 33 S | D |

|

|

| VSYNC |

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 0.01UF |

|

|

| 10UF/10V |

|

|

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 0.1UF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| A15 |

|

|

|

|

|

|

|

|

|

|

| G |

|

|

|

|

|

|

|

| ||||

| +3VS |

| L24 |

|

|

|

|

|

|

|

|

|

|

| DCLKAVSS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Q26 |

|

|

|

|

|

|

| ||||

|

|

|

| 6.49mA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

| FCM1608K121 |

|

|

| Z1XAVDD | W1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| +3VS |

|

|

|

|

|

|

|

| 2N7002 |

|

|

|

| +5VS | +5V | |||||

|

| 1 |

| 2 |

|

|

|

| Z1XAVDD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

| C93 |

|

|

| C96 |

| C97 |

|

|

|

|

|

| B14 | ECLKAVDD | 1 | L52 |

| 218.07mA |

|

|

|

|

|

|

| +3VS |

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

| 0.01UF |

|

|

|

|

|

| ECLKAVDD |

|

|

| FCM1608K121 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| R753 | 0 |

| ||||

| 10UF/10V |

|

| 0.1UF |

| Z1XAVSS | W2 |

|

|

|

|

|

|

|

|

| C287 | C271 |

|

|

| C265 |

|

|

|

|

|

| +3VS | +3VS |

|

|

|

|

| R754 | 0(R) |

| ||||

|

|

|

| 10MIL |

|

|

|

| Z1XAVSS |

|

|

|

|

|

|

| 0.01UF |

|

|

| 10UF/10V |

|

|

|

|

|

|

|

| +3VS |

|

|

|

|

| |||||||

|

| N7 |

|

|

|

|

|

|

|

|

|

|

|

| A14 | ECLKAVSS | 0.1UF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ECLKAVSS |

|

| 10MIL | N12 |

|

|

|

|

| R530 |

| R531 |

|

|

| R534 | R535 |

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| DLLEN# |

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||

| +3VS |

| L85 |

|

|

|

|

|

|

|

|

|

|

| DLLEN# | E11 | T |

|

|

|

|

|

|

|

|

|

| 4.7K |

|

| 4.7K |

| Q27 |

| 6.8K | 6.8K |

|

| ||||

|

| FCM1608K121 |

|

| 7.92mA |

| Z4XAVDD | V2 |

|

|

|

| C11 | TMODE0 |

|

|

|

|

|

|

|

|

|

|

|

|

| R532 | G |

|

|

|

|

| ||||||||

|

| 1 |

| 2 |

|

|

|

|

|

|

| TESTMODE0 | F11 | TMODE1 | T |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 2N7002 |

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

| Z4XAVDD |

|

| TESTMODE1 | A10 | TMODE2 | T |

|

|

|

|

|

|

|

|

| 30 VGADDCDATA |

|

| 33 | S | D | DDC1DATA |

|

|

| |||||

| C415 |

|

|

| C414 | C413 |

|

|

|

|

|

| TESTMODE2 |

|

|

| T |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

| 10UF/10V |

|

| 0.1UF |

| 0.01UF |

|

|

|

|

|

|

|

| E10 | TRAP0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| R533 | S | D | DDC1CLK |

|

|

| |||||

|

|

|

| Z4XAVSS | V1 |

|

|

|

| TRAP0 | T |

|

|

|

|

|

|

|

|

| 30 VGADDCCLK |

|

|

| 33 |

|

|

| ||||||||||||||

|

|

|

| 10MIL |

|

|

|

|

|

|

|

| D11 | TRAP1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

| Z4XAVSS |

|

| TRAP1 | F10 | ENTEST | T |

|

|

|

|

|

|

|

|

|

|

|

|

|

| G |

|

|

|

|

|

| ||||

|

| N15 |

|

|

|

|

|

|

|

|

|

|

|

| ENTEST |

|

|

| T |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Q28 |

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 2N7002 |

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| +3VS |

|

|

|

|

| |

30 | R | R |

| R693 |

| 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

G |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

30 | G |

| R694 |

| 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| D1 | F01J2E |

|

|

|

| +5VS |

|

|

|

|

|

|

|

|

| ||||

B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| C |

| A |

| +5VS |

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

| R695 |

| 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| VJVGA1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

30 | B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

ROUT |

|

|

|

|

|

|

|

|

|

|

|

|

|

| FRED_10 | CEN/VGA DSUB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

| R696 |

| 0(R) |

|

|

|

|

|

| R4 | FCM1608K121 |

|

| 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

| GOUT |

|

|

|

|

|

|

|

|

|

|

|

|

|

| FGRN_10 |

| 9 |

|

|

|

|

|

|

|

| R207 | R209 | R210 | R208 |

|

|

|

|

|

|

|

| |||

|

| R697 |

| 0(R) |

|

|

|

|

|

| R5 | FCM1608K121 |

|

| 2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

| BOUT |

|

|

|

|

|

|

|

|

|

|

|

|

|

| FBLU_10 |

| 10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

| R698 |

| 0(R) |

|

|

|

|

|

| R3 | FCM1608K121 |

|

| 3 |

|

|

|

|

|

|

|

|

| 2.2K(R)2.2K(R)4.7K(R) | 4.7K(R) |

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 11 |

| T |

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| T |

| 4 |

|

|

|

|

|

| L6 | FCM1608K121 |

|

|

| DDC1DATA |

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

| C7 | R200 | C8 | R199 | C6 | R201 |

|

|

|

|

| 12 |

| MID1_10 |

|

|

| 1 | 2 |

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| C243 | C242 | C245 |

| 5 |

|

| HS_10 |

|

|

|

| L45 | FCM1608K121 |

|

|

| HSYNC |

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 13 |

|

|

|

|

| 1 | 2 |

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

| 22P | 75 | 22P | 75 | 22P | 75 |

| 22P | 22P | 22P |

| 6 |

|

| VS_10 |

|

|

|

| L43 | FCM1608K121 |

|

|

| VSYNC |

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 14 |

|

|

|

|

| 1 | 2 |

|

|

|

|

|

|

|

|

| |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 7 |

|

| MID3_10 |

|

|

|

| FCM1608K121 |

|

|

| DDC1CLK |

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 15 |

|

|

|

| L44 1 | 2 |

|

|

|

|

|

|

|

|

| ||||||

|

|

|

| AC |

|

| AC |

|

|

| AC |

|

|

|

|

|

|

|

|

| 8 |

|

|

|

| C244 | C3 | C5 | C4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

| D2 |

|

| D3 |

|

| D21 |

|

|

|

|

|

|

| 17 16 |

|

|

|

| 220P | 220P | 220P | 220P |

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

| DA204U |

| DA204U |

|

| DA204U |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

| A | C |

| A | C |

|

| A | C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| +3VS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

B - 8 M645DX (& CRT Out) 3 of 4