Page

Page

Service Manual

Notebook Computer D900F

Preface

Preface

Trademarks

About this Manual

IMPORTANT SAFETY INSTRUCTIONS

This Computer’s Optical Device is a Laser Class 1 Product

Instructions for Care and Operation

Power Safety

5. Take care when using peripheral devices

Battery Precautions

Do not remove any batteries from the computer while it is powered on

Related Documents

VIII

Disassembly

Contents

Introduction

MXM3.0 PCI-E

1.Introduction

Chapter 1 Introduction

Overview

Introduction

BIOS

System Specifications

1 - 2 System Specifications

Processor

Battery

System Specifications 1

Power

Dimensions & Weight

1 - 4 External Locator - Top View with LCD Panel Open

External Locator - Top View with LCD Panel Open

Top View

Front Views

External Locator - Front & Right side Views

External Locator - Front & Right side Views 1

Right Side Views

Left Side View

External Locator - Left Side & Rear View

1 - 6 External Locator - Left Side & Rear View

Rear View

Bottom View

External Locator - Bottom View

External Locator - Bottom View 1

Overheating

1 - 8 Mainboard Overview - Top Key Parts

Mainboard Overview - Top Key Parts

Mainboard Top Key Parts

Mainboard Bottom

Mainboard Overview - Bottom Key Parts

Mainboard Overview - Bottom Key Parts 1

Key Parts

Mainboard Top Connectors

Mainboard Overview - Top Connectors

1 - 10 Mainboard Overview - Top Connectors

16 15

Mainboard Overview - Bottom Connectors 1

Mainboard Overview - Bottom Connectors

Mainboard Bottom Connectors

1.Introduction

Disassembly

Chapter 2 Disassembly

Overview

Overview

Connections

2.Disassembly

Maintenance Tools

2 - 2 Overview

Maintenance Precautions

Cleaning

Disassembly Steps

Battery Removal

Removing the Battery

Removing the Battery

a. Loosen screws b. Release the battery

2 - 6 Removing the Optical CD/DVD Device

Removing the Optical CD/DVD Device

Optical Device Removal

HDD Assembly Removal

Removing the Hard Disk Drive

Removing the Hard Disk Drive 2

Removing the Hard Disks in the Secondary HDD Bay

Secondary HDD Assembly Removal

3. Hard Disk Assembly

2 - 8 Removing the Hard Disk Drive

Removing the Keyboard 2

Removing the Keyboard

Keyboard Tabs

Keyboard Removal

Removing the System Memory RAM

2 - 10 Removing the System Memory RAM

Removing the System Memory RAM 2

RAM Module Removal cont’d

Third RAM Module Removal

Upgrading a Third System Memory RAM Module

2 - 12 Removing the System Memory RAM

2 Screws

Disassembly

2 - 14 Removing the Processor

Removing the Processor

Processor Removal

VGA Card Removal

Removing the VGA Card

Removing the VGA Card 2

17 Screws

2 - 16 Removing the VGA Card

VGA Card Removal cont’d

Installing the VGA Card

VGA Card Installation

2 - 18 Removing the Wireless LAN Module

Removing the Wireless LAN Module

Wireless LAN Module Removal

Removing the Bluetooth Module 2

Removing the Bluetooth Module

Bluetooth Module Removal

2 - 20 Removing the Modem

Removing the Modem

Modem Removal

Removing the TV Tuner Card 2

Removing the TV Tuner Card

TV Tuner Card Removal

2 - 22 Removing the Intel Turbo Memory Card

Removing the Intel Turbo Memory Card

Intel Turbo Memory Card Removal

A.Part Lists

Appendix A Part Lists

Part Lists

A - 2 Part List Illustration Location

Part List Illustration Location

Table A

Part List Illustration Location

㥽䈜㾲䈷

Figure A

Top A

㪾䒅 㾲䈷

Bottom

Bottom

A - 4 Bottom

㾲䈷 㾲䈷

㾲䈷 㾲䈷 㾲䈷 㾲䈷 㾲䈷 㾲䈷 㾲䈷 㾲䈷 㾲䈷 㾲䈷 㳰㛨䨑㛽㾲䈷 㾲䈷 㾲䈷 褜㬘㾲䈷 㾲䈷䐈㗱㗺㖛㟯㧹 㾲䈷 㾲䈷 褜㬘 㾲䈷

LCD A

㾲䈷䐈㗱㗺㟯㧹 㾲䈷 㺉䧰 㙰䕊㾲䈷 㾲䈷 㾲䈷 ー㞁褜㾲䈷 㾲䈷 䐥㴆㞝䧰㾲䈷 褜㬘 㾲䈷 㾲䈷 㾲䈷 褜㬘 㾲䈷 㾲䈷

Mainboard

Mainboard

A - 6 Mainboard

㾲䈷 㾲䈷 㾲䈷 㾲䈷 㾲䈷 㾲䈷 㾲䈷 䠂㖨㖃䏧 㾲䈷 㾲䈷 㗸㗺㾲䈷 㗸㗺㾲䈷

Blu-Ray Combo

Blu-Ray Combo

Blu-Ray Combo A

㾲䈷 㾲䈷 㾲䈷 㾲䈷 㾲䈷 㾲䈷

A - 8 DVD Super Multi

DVD Super Multi

DVD Super Multi

Schematic Diagrams

Appendix B Schematic Diagrams

B.Schematic Diagrams

Schematic Diagrams

B - 2 System Block Diagram

System Block Diagram

CLEVO D900F System Block Diagram

Diagram

Sheet 2 of LGA1366 Part A DDR3 1/2

LGA1366 Part A DDR3 1/2

LGA1366 Part A DDR3 1/2 B

ChannelA

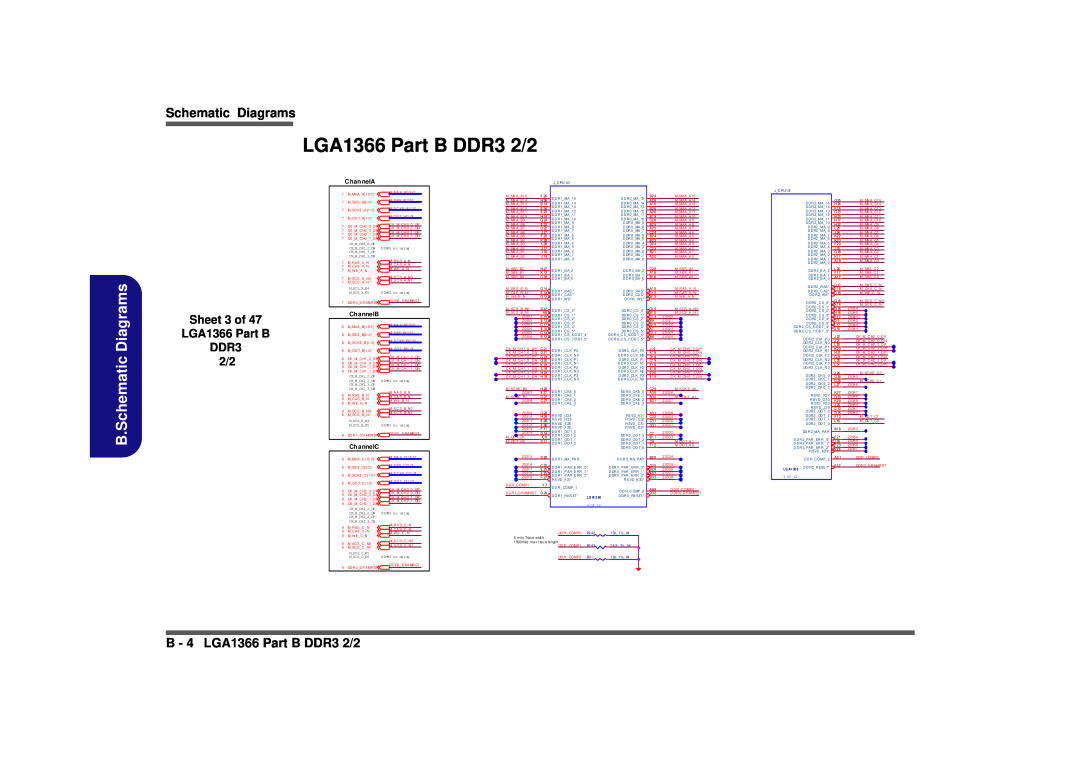

Sheet 3 of

LGA1366 Part B DDR3 2/2

B - 4 LGA1366 Part B DDR3 2/2

LGA1366 Part B DDR3 2/2

Diagrams

B.Schematic

LGA1366 Part C QPI

LGA1366 Part C QPI B

Sheet 5 of LGA1366 Part C Power

LGA1366 Part C Power

B - 6 LGA1366 Part C Power

CAD NOTE

LGA1366 Part E GND, Thermal B

LGA1366 Part E GND, Thermal

Place near to the CPU

Sheet 6 of LGA1366 Part E GND, Thermal

B - 8 DDR3 Channel A SO-DIMM0

DDR3 Channel A SO-DIMM0

ChannelA

Sheet 7 of DDR3 Channel A SO-DIMM0

ChannelB

B.Schematic Diagrams

DDR3 Channel B SO-DIMM1

DDR3 Channel B SO-DIMM1 B

B - 10 DDR3 Channel C SO-DIMM2

DDR3 Channel C SO-DIMM2

ChannelC

Sheet 9 of DDR3 Channel C SO-DIMM2

X58 QPI Interface B

X58 QPI Interface

GT/s De fault

X58 QPI Interface

PCIEX162 D900B none using now

X58 PCIEX16, PCIEX4, DMI

B.Schematic Diagrams

PCIEX4 D900B none using now

Sheet 12 of X58 Misc

X58 Misc

X58 Misc B

6 OF

B - 14 X58 PWR

X58 PWR

Sheet 13 of X58 PWR

X58 GND B

X58 GND

B.Schematic

Sheet 14 of

ICH10 DMI/PCIE/USB/SATA

Diagrams

B.Schematic

POWER OK

Sheet 16 of ICH10 PCI/SPI Other

ICH10 PCI/SPI/Other

ICH10 PCI/SPI/Other B

Zo= 55O?

Sheet 17 of ICH10 Power/GND

ICH10 Power/GND

B - 18 ICH10 Power/GND

VCCHDA

Intel Debug Card & Fan Control B

Intel Debug Card & Fan Control

Schematic

Sheet 18 of

Sheet 19 of Clock Generator CV193

Clock Generator CV193

B - 20 Clock Generator CV193

SRC7..0

B.SchematicDiagrams

MXM3.0 PCI-E

Schematic Diagrams

MXM3.0 PCI-E B

Sheet 21 of MXM PWR, SATA ODD

MXM PWR, SATA ODD

B - 22 MXM PWR, SATA ODD

MXM PWR

HDMI & e-SATA B

HDMI & e-SATA

HDMI SWITCH

HDMI

B - 24 DVI-I

DVI-I

PLEASE CLOSE TO CONNECTOR

DVI-I

0.01uF for LVDS power time

Schematic

LCD, INT

LCD, INT B

B - 26 Card Reader/1394

Card Reader/1394

IEEE13941394

Sheet 25 of Card Reader/1394

DATASHEET? 1.2V? ? ?

RTL8111C

Schematic Diagrams

Hi Enable

Sheet 27 of 47 ALC662 / AMP TPA6047A4

ALC662 / AMP TP6047A-4

B - 28 ALC662 / AMP TP6047A-4

FRONT CHANNEL 2W

Sheet 28 of

KBC-ITE IT8512E

KBC-ITE IT8512E B

KBC-ITE IT8512E

LPC reset timing

Mini WLAN/ TMP/ TPA6017A2

Disable TPM function

B - 30 Mini WLAN/ TMP/ TPA6017A2

CLICK BOARD

Daughter CONN

PHONE JACK BOARD

SWITCH BOARD

B - 32 SATA HDD/ CCD/ BT/ PC BEEP

SATA HDD/ CCD/ BT/ PC BEEP

Bluetooth

Sheet 31 of SATA HDD/ CCD BT/ PC BEEP

New Card/ mDC

New Card/ MDC/ TV/ Robson

New Card/ MDC/ TV/ Robson B

NEW CARD

Sheet 33 of Audio Board

Audio Board

B - 34 Audio Board

LINE IN

Card Reader Board B

Card Reader Board

Sheet 34 of Card Reader Board

Sheet 35 of Click Board

Click Board

B - 36 Click Board

10MIL

Sheet 36 of Hotkey Board

Hotkey Board

Hotkey Board B

SPI FLASH TOOL

B - 38 Switch Board

Switch Board

Diagrams

Sheet 37 of 47 Switch Board

USB Board B

USB Board

EMI solution,when placement

Sheet 38 of USB Board

ISL6314CR POWER CKT

Power CPUVTT

B - 40 Power CPUVTT

Sheet 39 of Power CPUVTT

Power

Power 1.5V, 0.75VS

Power 1.5V, 0.75VS, 12V B

0.75VS

Power 1.8VS, 1.1VS

Power 1.8VS, 1.1VS

B - 42 Power 1.8VS, 1.1VS

Sheet 41 of

POWER

Power ACIn, Charge

Power ACIn, Charge B

AC IN & CHARGER

Power Switch

Power Switch, ICH1.1VS

B - 44 Power Switch, ICH1.1VS

ICH1.1VS

Sheet 44 of Power VCORE

Power VCORE

Power VCORE B

NCP5392 Intel VRD11.1 POWER CKT

Sheet 45 of Power VDD3, VDD5

Power VDD3, VDD5

B - 46 Power VDD3, VDD5

VDD3,VDD5

Power Delivery Chart B

Power Delivery Chart

Sheet 46 of Power Delivery Chart

Sheet 47 of Power Sequence Diagram

Power Sequence Diagram

B - 48 Power Sequence Diagram

D900F V0.0 BOOT