|

|

| CY14B101Q1 | |

|

|

| ||

|

| PRELIMINARY | CY14B101Q2 | |

|

| CY14B101Q3 | ||

|

|

|

|

|

|

|

|

|

|

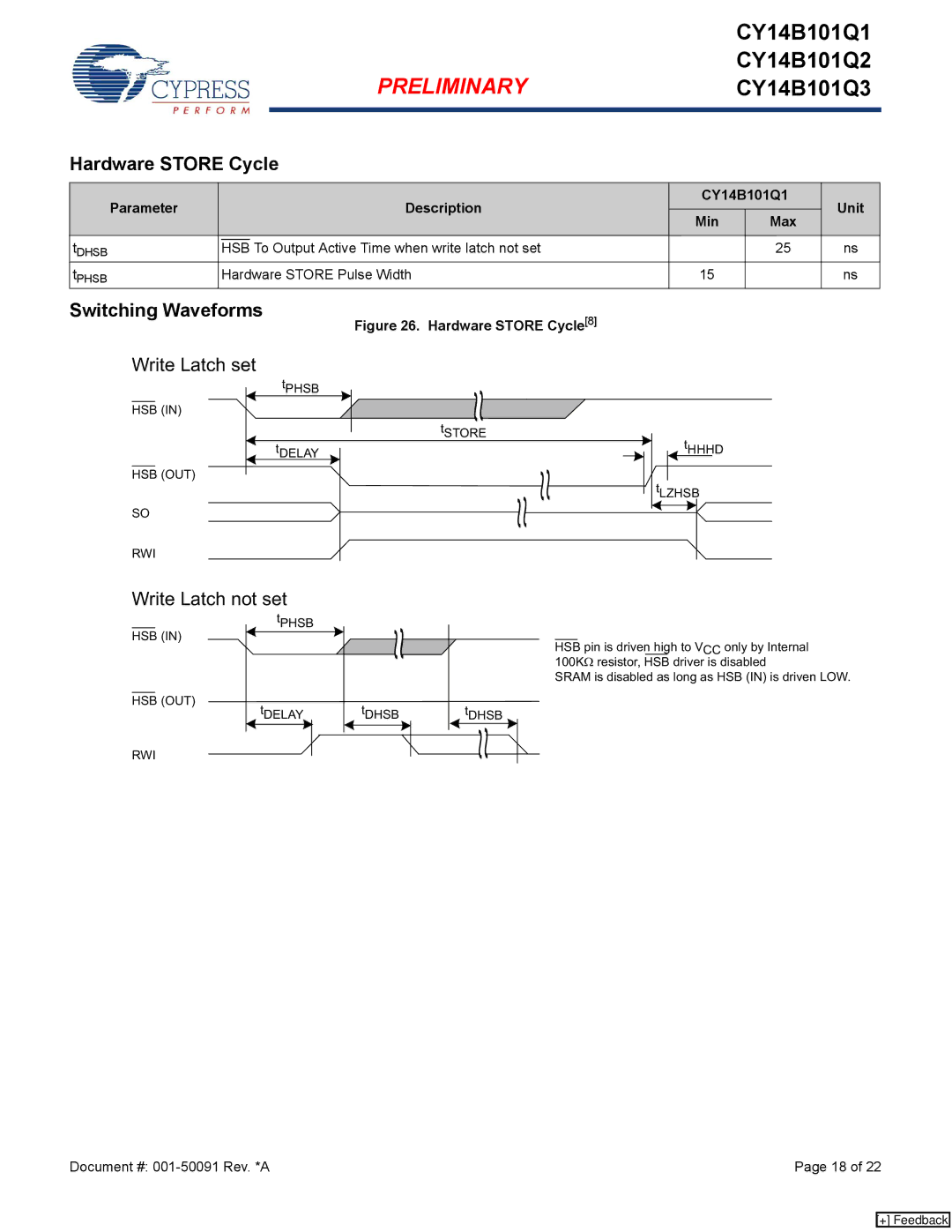

Hardware STORE Cycle

Parameter |

|

| Description | CY14B101Q1 | Unit | |

|

| Min | Max | |||

|

|

|

|

| ||

tDHSB |

|

| To Output Active Time when write latch not set |

| 25 | ns |

HSB |

| |||||

tPHSB |

| Hardware STORE Pulse Width | 15 |

| ns | |

Switching Waveforms

Write Latch set

tPHSB

HSB (IN)

tDELAY

HSB (OUT)

SO

RWI

Figure 26. Hardware STORE Cycle[8]

~ ~ |

|

tSTORE | ~ |

~~ | |

| ~ |

tHHHD

tLZHSB

Write Latch not set

tPHSB

HSB (IN)

HSB | (OUT) | tDELAY |

|

| |

RWI |

| |

~ ~

tDHSB

HSB pin is driven high to VCC only by Internal 100K: resistor, HSB driver is disabled

SRAM is disabled as long as HSB (IN) is driven LOW.

tDHSB |

~ ~ |

Document #: | Page 18 of 22 |

[+] Feedback