CY14B101Q1

CY14B101Q2

PRELIMINARYCY14B101Q3

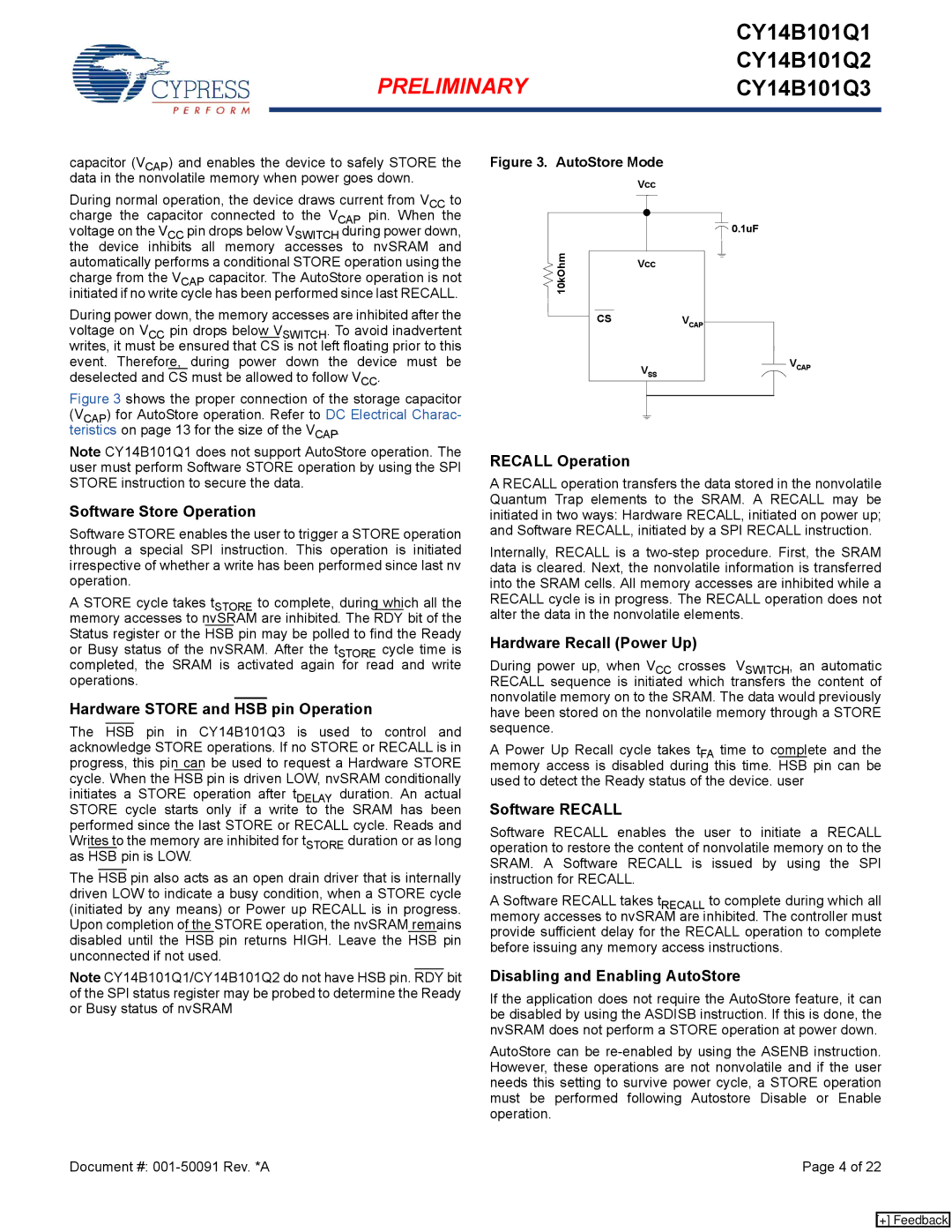

capacitor (VCAP) and enables the device to safely STORE the | Figure 3. AutoStore Mode |

data in the nonvolatile memory when power goes down. | Vcc |

|

During normal operation, the device draws current from VCC to charge the capacitor connected to the VCAP pin. When the voltage on the VCC pin drops below VSWITCH during power down, the device inhibits all memory accesses to nvSRAM and automatically performs a conditional STORE operation using the charge from the VCAP capacitor. The AutoStore operation is not initiated if no write cycle has been performed since last RECALL.

During power down, the memory accesses are inhibited after the voltage on VCC pin drops below VSWITCH. To avoid inadvertent writes, it must be ensured that CS is not left floating prior to this event. Therefore, during power down the device must be deselected and CS must be allowed to follow VCC.

Figure 3 shows the proper connection of the storage capacitor (VCAP) for AutoStore operation. Refer to DC Electrical Charac- teristics on page 13 for the size of the VCAP.

Note CY14B101Q1 does not support AutoStore operation. The user must perform Software STORE operation by using the SPI STORE instruction to secure the data.

Software Store Operation

Software STORE enables the user to trigger a STORE operation through a special SPI instruction. This operation is initiated irrespective of whether a write has been performed since last nv operation.

A STORE cycle takes tSTORE to complete, during which all the memory accesses to nvSRAM are inhibited. The RDY bit of the Status register or the HSB pin may be polled to find the Ready or Busy status of the nvSRAM. After the tSTORE cycle time is completed, the SRAM is activated again for read and write operations.

Hardware STORE and HSB pin Operation

The HSB pin in CY14B101Q3 is used to control and acknowledge STORE operations. If no STORE or RECALL is in progress, this pin can be used to request a Hardware STORE cycle. When the HSB pin is driven LOW, nvSRAM conditionally initiates a STORE operation after tDELAY duration. An actual STORE cycle starts only if a write to the SRAM has been performed since the last STORE or RECALL cycle. Reads and Writes to the memory are inhibited for tSTORE duration or as long as HSB pin is LOW.

The HSB pin also acts as an open drain driver that is internally driven LOW to indicate a busy condition, when a STORE cycle (initiated by any means) or Power up RECALL is in progress. Upon completion of the STORE operation, the nvSRAM remains disabled until the HSB pin returns HIGH. Leave the HSB pin unconnected if not used.

10kOhm | 0.1uF | |

Vcc | ||

| ||

CS | VCAP | |

| VCAP | |

| VSS |

RECALL Operation

A RECALL operation transfers the data stored in the nonvolatile Quantum Trap elements to the SRAM. A RECALL may be initiated in two ways: Hardware RECALL, initiated on power up; and Software RECALL, initiated by a SPI RECALL instruction.

Internally, RECALL is a

Hardware Recall (Power Up)

During power up, when VCC crosses VSWITCH, an automatic RECALL sequence is initiated which transfers the content of nonvolatile memory on to the SRAM. The data would previously have been stored on the nonvolatile memory through a STORE sequence.

A Power Up Recall cycle takes tFA time to complete and the memory access is disabled during this time. HSB pin can be used to detect the Ready status of the device. user

Software RECALL

Software RECALL enables the user to initiate a RECALL operation to restore the content of nonvolatile memory on to the SRAM. A Software RECALL is issued by using the SPI instruction for RECALL.

A Software RECALL takes tRECALL to complete during which all memory accesses to nvSRAM are inhibited. The controller must provide sufficient delay for the RECALL operation to complete before issuing any memory access instructions.

Note CY14B101Q1/CY14B101Q2 do not have HSB pin. RDY bit of the SPI status register may be probed to determine the Ready or Busy status of nvSRAM

Disabling and Enabling AutoStore

If the application does not require the AutoStore feature, it can be disabled by using the ASDISB instruction. If this is done, the nvSRAM does not perform a STORE operation at power down.

AutoStore can be

Document #: | Page 4 of 22 |

[+] Feedback