|

|

|

|

|

| PRELIMINARY |

|

| CY14B108K, CY14B108M | |||||||

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

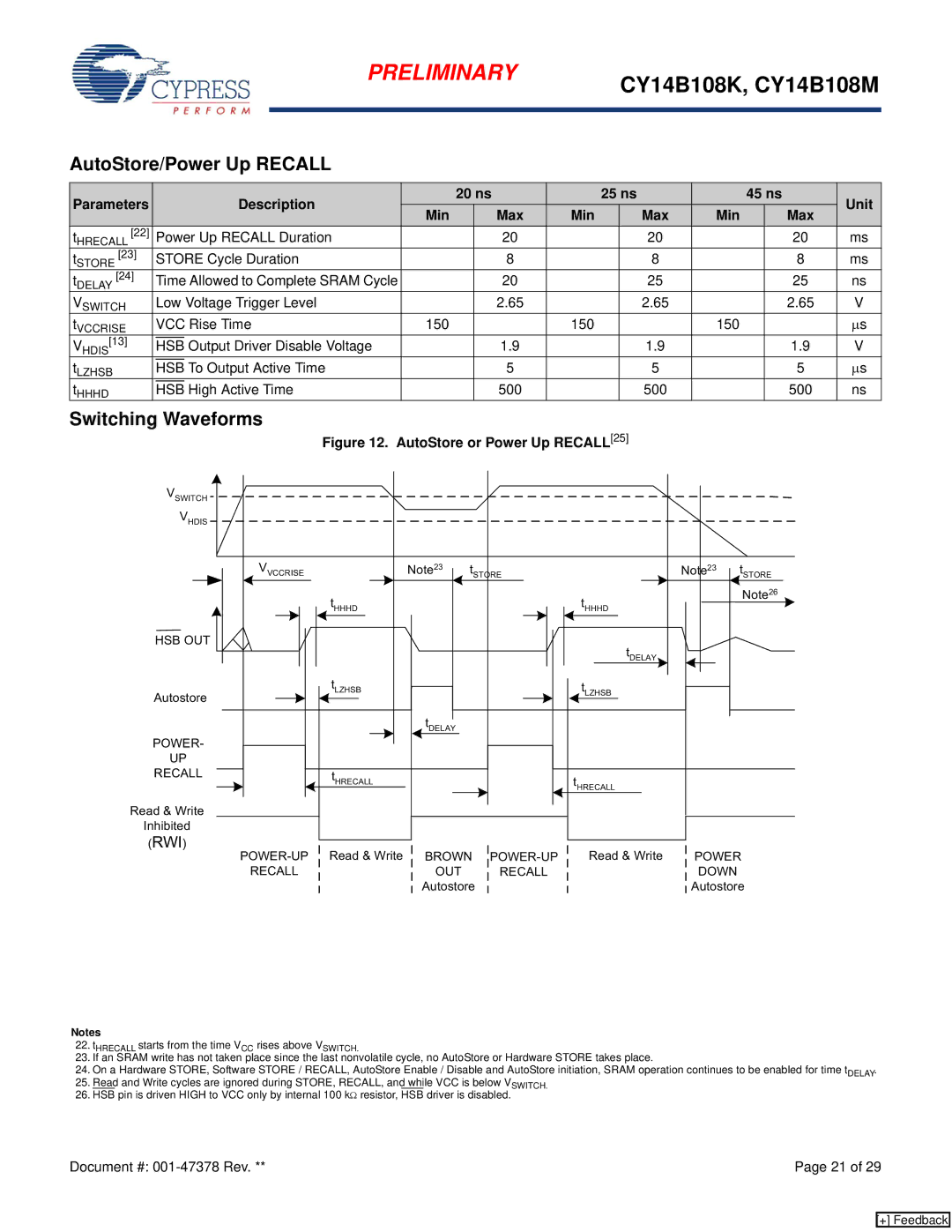

AutoStore/Power Up RECALL |

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Parameters |

|

| Description |

| 20 ns |

| 25 ns |

| 45 ns | Unit | ||||||

|

| Min |

| Max | Min |

| Max | Min |

| Max | ||||||

|

|

|

|

|

|

|

|

|

|

| ||||||

t | [22] |

| Power Up RECALL Duration |

|

| 20 |

|

| 20 |

|

| 20 | ms | |||

HRECALL |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tSTORE [23] |

| STORE Cycle Duration |

|

| 8 |

|

| 8 |

|

| 8 | ms | ||||

tDELAY [24] |

| Time Allowed to Complete SRAM Cycle |

|

| 20 |

|

| 25 |

|

| 25 | ns | ||||

VSWITCH |

|

| Low Voltage Trigger Level |

|

| 2.65 |

|

| 2.65 |

|

| 2.65 | V | |||

tVCCRISE |

|

| VCC Rise Time | 150 |

|

| 150 |

|

| 150 |

|

| μs | |||

VHDIS[13] |

|

|

| Output Driver Disable Voltage |

|

| 1.9 |

|

| 1.9 |

|

| 1.9 | V | ||

|

| HSB |

|

|

| |||||||||||

tLZHSB |

|

|

| To Output Active Time |

|

| 5 |

|

| 5 |

|

| 5 | μs | ||

|

| HSB |

|

|

| |||||||||||

tHHHD |

|

|

| High Active Time |

|

| 500 |

|

| 500 |

|

| 500 | ns | ||

|

| HSB |

|

|

| |||||||||||

Switching Waveforms

Figure 12. AutoStore or Power Up RECALL[25]

VSWITCH |

|

|

|

|

VHDIS |

|

|

|

|

VVCCRISE | Note23 | t | Note23 | t |

|

| STORE |

| STORE |

| tHHHD |

| tHHHD | Note26 |

|

|

| ||

HSB OUT |

|

| tDELAY |

|

|

|

|

| |

| tLZHSB |

| t |

|

Autostore |

|

| LZHSB |

|

|

|

|

| |

| tDELAY |

|

|

|

POWER- |

|

|

|

|

UP |

|

|

|

|

RECALL | tHRECALL |

| tHRECALL |

|

|

|

|

|

Read & Write

Inhibited

(RWI)

BROWN | Read & Write | POWER | ||

RECALL | OUT | RECALL |

| DOWN |

| Autostore |

|

| Autostore |

Notes

22.tHRECALL starts from the time VCC rises above VSWITCH.

23.If an SRAM write has not taken place since the last nonvolatile cycle, no AutoStore or Hardware STORE takes place.

24.On a Hardware STORE, Software STORE / RECALL, AutoStore Enable / Disable and AutoStore initiation, SRAM operation continues to be enabled for time tDELAY.

25.Read and Write cycles are ignored during STORE, RECALL, and while VCC is below VSWITCH.

26.HSB pin is driven HIGH to VCC only by internal 100 kΩ resistor, HSB driver is disabled.

Document #: | Page 21 of 29 |

[+] Feedback