CY7C1141V18, CY7C1156V18

CY7C1143V18, CY7C1145V18

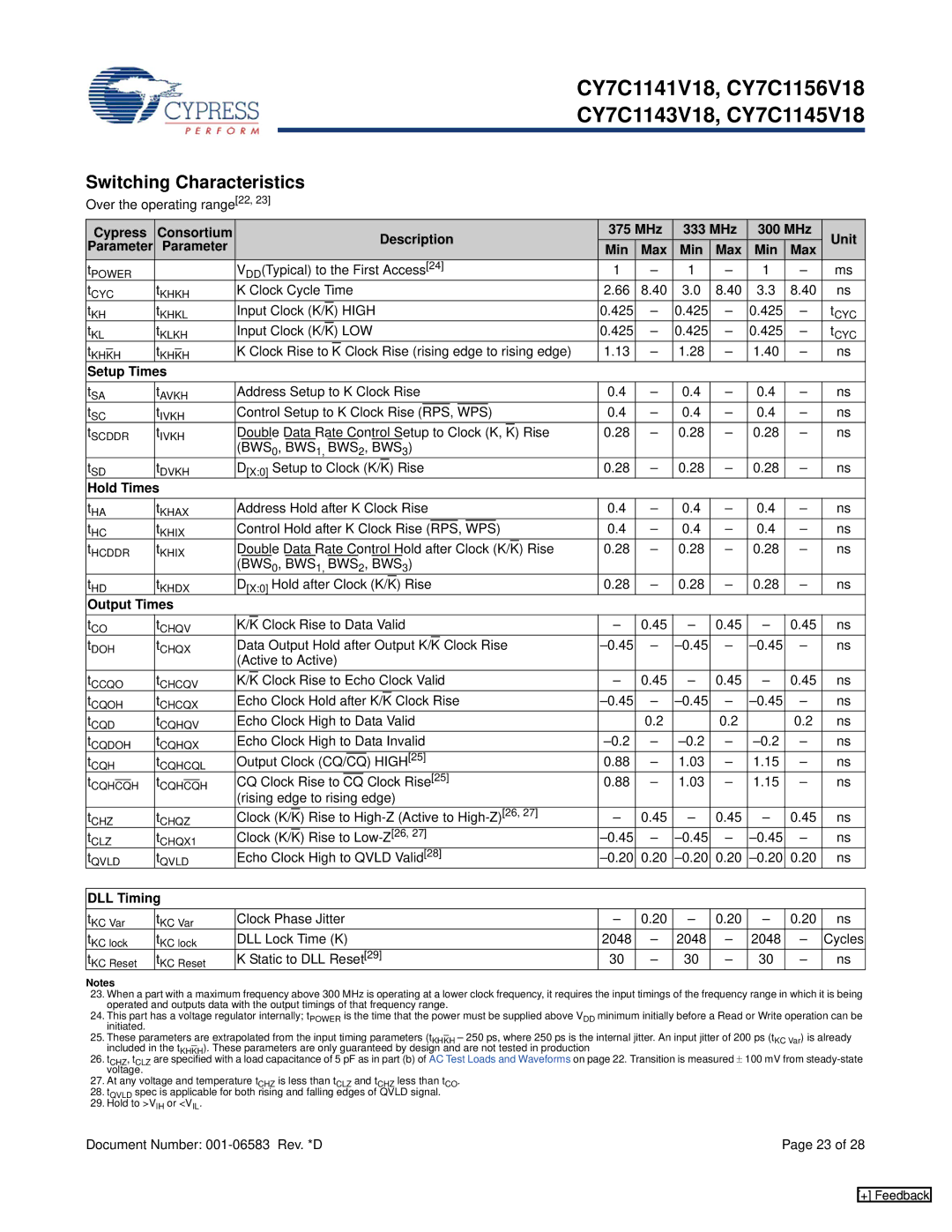

Switching Characteristics

Over the operating range[22, 23]

Cypress | Consortium |

|

|

|

|

|

|

|

|

|

|

|

|

| Description | 375 MHz | 333 MHz | 300 MHz | Unit | |||||||||||||||||||||||||

Parameter | Parameter |

|

|

|

|

|

|

|

|

|

|

|

|

| Min | Max | Min | Max | Min | Max | ||||||||||||||||||||||||

tPOWER |

|

| VDD(Typical) to the First Access[24] | 1 | – | 1 | – | 1 | – | ms | ||||||||||||||||||||||||||||||||||

tCYC | tKHKH | K Clock Cycle Time | 2.66 | 8.40 | 3.0 | 8.40 | 3.3 | 8.40 | ns | |||||||||||||||||||||||||||||||||||

tKH | tKHKL | Input Clock (K/K) |

| HIGH | 0.425 | – | 0.425 | – | 0.425 | – | tCYC | |||||||||||||||||||||||||||||||||

tKL | tKLKH | Input Clock (K/K) |

| LOW | 0.425 | – | 0.425 | – | 0.425 | – | tCYC | |||||||||||||||||||||||||||||||||

tKHKH | tKHKH | K Clock Rise to | K |

| Clock Rise (rising edge to rising edge) | 1.13 | – | 1.28 | – | 1.40 | – | ns | ||||||||||||||||||||||||||||||||

Setup Times |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

tSA | tAVKH | Address Setup to K Clock Rise | 0.4 | – | 0.4 | – | 0.4 | – | ns | |||||||||||||||||||||||||||||||||||

tSC | tIVKH | Control Setup to K Clock Rise | (RPS, |

| WPS) |

|

|

|

|

|

| 0.4 | – | 0.4 | – | 0.4 | – | ns | ||||||||||||||||||||||||||

tSCDDR | tIVKH | Double Data Rate Control Setup to Clock (K, | K) Rise | 0.28 | – | 0.28 | – | 0.28 | – | ns | ||||||||||||||||||||||||||||||||||

|

|

|

| (BWS0, BWS1, BWS2, BWS3) |

|

|

|

|

|

|

| |||||||||||||||||||||||||||||||||

tSD | tDVKH | D[X:0] Setup to Clock (K/K) |

|

| Rise | 0.28 | – | 0.28 | – | 0.28 | – | ns | ||||||||||||||||||||||||||||||||

Hold Times |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

tHA | tKHAX | Address Hold after K Clock Rise | 0.4 | – | 0.4 | – | 0.4 | – | ns | |||||||||||||||||||||||||||||||||||

tHC | tKHIX | Control Hold after K Clock Rise | (RPS, |

| WPS) |

|

|

| 0.4 | – | 0.4 | – | 0.4 | – | ns | |||||||||||||||||||||||||||||

tHCDDR | tKHIX | Double Data Rate Control Hold after Clock (K/K) | Rise | 0.28 | – | 0.28 | – | 0.28 | – | ns | ||||||||||||||||||||||||||||||||||

|

|

|

| (BWS0, BWS1, BWS2, BWS3) |

|

|

|

|

|

|

| |||||||||||||||||||||||||||||||||

tHD | tKHDX | D[X:0] Hold after Clock (K/K) | Rise | 0.28 | – | 0.28 | – | 0.28 | – | ns | ||||||||||||||||||||||||||||||||||

Output Times |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

tCO | tCHQV | K/K | Clock Rise to Data Valid | – | 0.45 | – | 0.45 | – | 0.45 | ns | ||||||||||||||||||||||||||||||||||

tDOH | tCHQX | Data Output Hold after Output K/K | Clock Rise | – | – | – | ns | |||||||||||||||||||||||||||||||||||||

|

|

|

| (Active to Active) |

|

|

|

|

|

|

| |||||||||||||||||||||||||||||||||

tCCQO | tCHCQV | K/K | Clock Rise to Echo Clock Valid | – | 0.45 | – | 0.45 | – | 0.45 | ns | ||||||||||||||||||||||||||||||||||

tCQOH | tCHCQX | Echo Clock Hold after K/K | Clock Rise | – | – | – | ns | |||||||||||||||||||||||||||||||||||||

tCQD | tCQHQV | Echo Clock High to Data Valid |

| 0.2 |

| 0.2 |

| 0.2 | ns | |||||||||||||||||||||||||||||||||||

tCQDOH | tCQHQX | Echo Clock High to Data Invalid | – | – | – | ns | ||||||||||||||||||||||||||||||||||||||

tCQH | tCQHCQL | Output Clock (CQ/CQ) | HIGH[25] | 0.88 | – | 1.03 | – | 1.15 | – | ns | ||||||||||||||||||||||||||||||||||

tCQHCQH |

| tCQHCQH |

| CQ Clock Rise to | CQ | Clock Rise[25] | 0.88 | – | 1.03 | – | 1.15 | – | ns | |||||||||||||||||||||||||||||||

|

|

|

| (rising edge to rising edge) |

|

|

|

|

|

|

| |||||||||||||||||||||||||||||||||

tCHZ | tCHQZ | Clock (K/K) | Rise to | – | 0.45 | – | 0.45 | – | 0.45 | ns | ||||||||||||||||||||||||||||||||||

tCLZ | tCHQX1 | Clock (K/K) | Rise to | – | – | – | ns | |||||||||||||||||||||||||||||||||||||

tQVLD | tQVLD | Echo Clock High to QVLD Valid[28] | 0.20 | 0.20 | 0.20 | ns | ||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

DLL Timing |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

tKC Var | tKC Var | Clock Phase Jitter | – | 0.20 | – | 0.20 | – | 0.20 | ns | |||||||||||||||||||||||||||||||||||

tKC lock | tKC lock | DLL Lock Time (K) | 2048 | – | 2048 | – | 2048 | – | Cycles | |||||||||||||||||||||||||||||||||||

tKC Reset | tKC Reset | K Static to DLL Reset[29] | 30 | – | 30 | – | 30 | – | ns | |||||||||||||||||||||||||||||||||||

Notes

23.When a part with a maximum frequency above 300 MHz is operating at a lower clock frequency, it requires the input timings of the frequency range in which it is being operated and outputs data with the output timings of that frequency range.

24.This part has a voltage regulator internally; tPOWER is the time that the power must be supplied above VDD minimum initially before a Read or Write operation can be initiated.

25.These parameters are extrapolated from the input timing parameters (tKHKH – 250 ps, where 250 ps is the internal jitter. An input jitter of 200 ps (tKC Var) is already included in the tKHKH). These parameters are only guaranteed by design and are not tested in production

26.tCHZ, tCLZ are specified with a load capacitance of 5 pF as in part (b) of AC Test Loads and Waveforms on page 22. Transition is measured ± 100 mV from

27.At any voltage and temperature tCHZ is less than tCLZ and tCHZ less than tCO.

28.tQVLD spec is applicable for both rising and falling edges of QVLD signal.

29.Hold to >VIH or <VIL.

Document Number: | Page 23 of 28 |

[+] Feedback