CY7C1215H

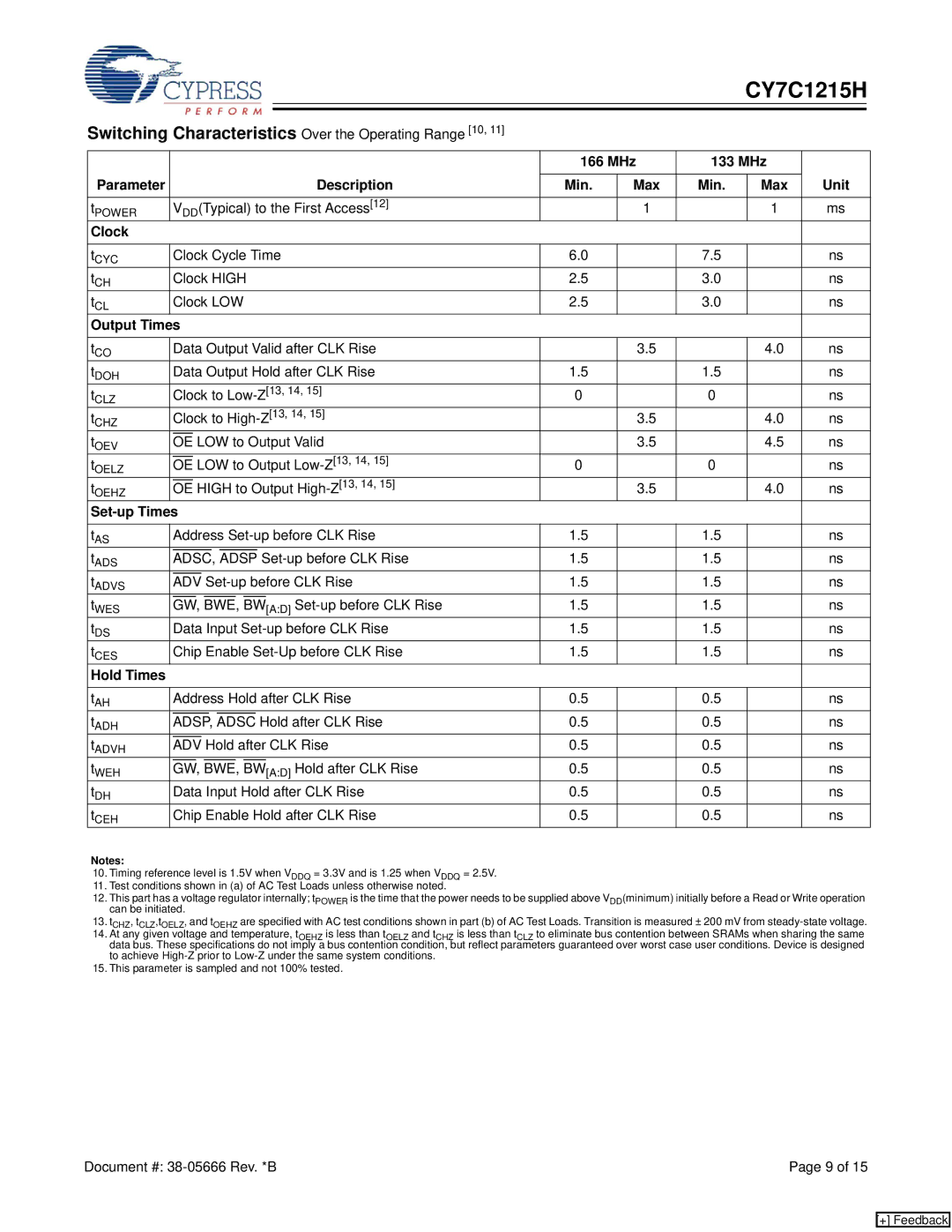

Switching Characteristics Over the Operating Range [10, 11]

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 166 MHz | 133 MHz |

| ||

Parameter |

|

|

|

|

|

|

|

|

|

|

|

|

|

| Description |

|

|

|

| Unit |

|

|

|

|

|

|

|

|

|

|

|

|

|

| Min. | Max | Min. | Max | |||

|

|

|

|

|

|

|

| |||||||||||||

tPOWER |

| VDD(Typical) to the First Access[12] |

| 1 |

| 1 | ms | |||||||||||||

Clock |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

| ||||||||||||||

tCYC |

| Clock Cycle Time | 6.0 |

| 7.5 |

| ns | |||||||||||||

tCH |

| Clock HIGH | 2.5 |

| 3.0 |

| ns | |||||||||||||

tCL |

| Clock LOW | 2.5 |

| 3.0 |

| ns | |||||||||||||

Output Times |

|

|

|

|

| |||||||||||||||

|

|

|

|

|

|

| ||||||||||||||

tCO |

| Data Output Valid after CLK Rise |

| 3.5 |

| 4.0 | ns | |||||||||||||

tDOH |

| Data Output Hold after CLK Rise | 1.5 |

| 1.5 |

| ns | |||||||||||||

t |

| Clock to | 0 |

| 0 |

| ns | |||||||||||||

CLZ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

| Clock to |

| 3.5 |

| 4.0 | ns | |||||||||||||

CHZ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tOEV |

|

|

| LOW to Output Valid |

| 3.5 |

| 4.5 | ns | |||||||||||

OE |

|

| ||||||||||||||||||

tOELZ |

|

|

| LOW to Output | 0 |

| 0 |

| ns | |||||||||||

OE |

|

| ||||||||||||||||||

tOEHZ |

|

|

| HIGH to Output |

| 3.5 |

| 4.0 | ns | |||||||||||

OE |

|

| ||||||||||||||||||

|

|

|

|

|

| |||||||||||||||

|

|

|

|

|

|

| ||||||||||||||

tAS |

| Address | 1.5 |

| 1.5 |

| ns | |||||||||||||

tADS |

|

|

|

|

|

|

|

|

|

|

|

|

| 1.5 |

| 1.5 |

| ns | ||

ADSC, | ADSP |

|

| |||||||||||||||||

tADVS |

|

|

|

|

| 1.5 |

| 1.5 |

| ns | ||||||||||

ADV |

|

| ||||||||||||||||||

tWES |

|

|

|

|

|

|

|

|

|

|

|

|

| [A:D] | 1.5 |

| 1.5 |

| ns | |

GW, | BWE, | BW |

|

| ||||||||||||||||

tDS |

| Data Input | 1.5 |

| 1.5 |

| ns | |||||||||||||

tCES |

| Chip Enable | 1.5 |

| 1.5 |

| ns | |||||||||||||

Hold Times |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

| ||||||||||||||

tAH |

| Address Hold after CLK Rise | 0.5 |

| 0.5 |

| ns | |||||||||||||

tADH |

|

|

|

|

|

|

|

|

|

|

| Hold after CLK Rise | 0.5 |

| 0.5 |

| ns | |||

ADSP, | ADSC |

|

| |||||||||||||||||

tADVH |

|

|

|

| Hold after CLK Rise | 0.5 |

| 0.5 |

| ns | ||||||||||

ADV |

|

| ||||||||||||||||||

tWEH |

|

|

|

|

|

|

|

|

|

|

|

|

| [A:D] Hold after CLK Rise | 0.5 |

| 0.5 |

| ns | |

GW, | BWE, | BW |

|

| ||||||||||||||||

tDH |

| Data Input Hold after CLK Rise | 0.5 |

| 0.5 |

| ns | |||||||||||||

tCEH |

| Chip Enable Hold after CLK Rise | 0.5 |

| 0.5 |

| ns | |||||||||||||

Notes:

10.Timing reference level is 1.5V when VDDQ = 3.3V and is 1.25 when VDDQ = 2.5V.

11.Test conditions shown in (a) of AC Test Loads unless otherwise noted.

12.This part has a voltage regulator internally; tPOWER is the time that the power needs to be supplied above VDD(minimum) initially before a Read or Write operation can be initiated.

13.tCHZ, tCLZ,tOELZ, and tOEHZ are specified with AC test conditions shown in part (b) of AC Test Loads. Transition is measured ± 200 mV from

14.At any given voltage and temperature, tOEHZ is less than tOELZ and tCHZ is less than tCLZ to eliminate bus contention between SRAMs when sharing the same data bus. These specifications do not imply a bus contention condition, but reflect parameters guaranteed over worst case user conditions. Device is designed to achieve

15.This parameter is sampled and not 100% tested.

Document #: | Page 9 of 15 |

[+] Feedback