|

|

|

|

|

|

| CY7C1292DV18 |

|

|

|

|

|

|

|

| CY7C1294DV18 |

|

|

|

|

|

|

|

|

|

|

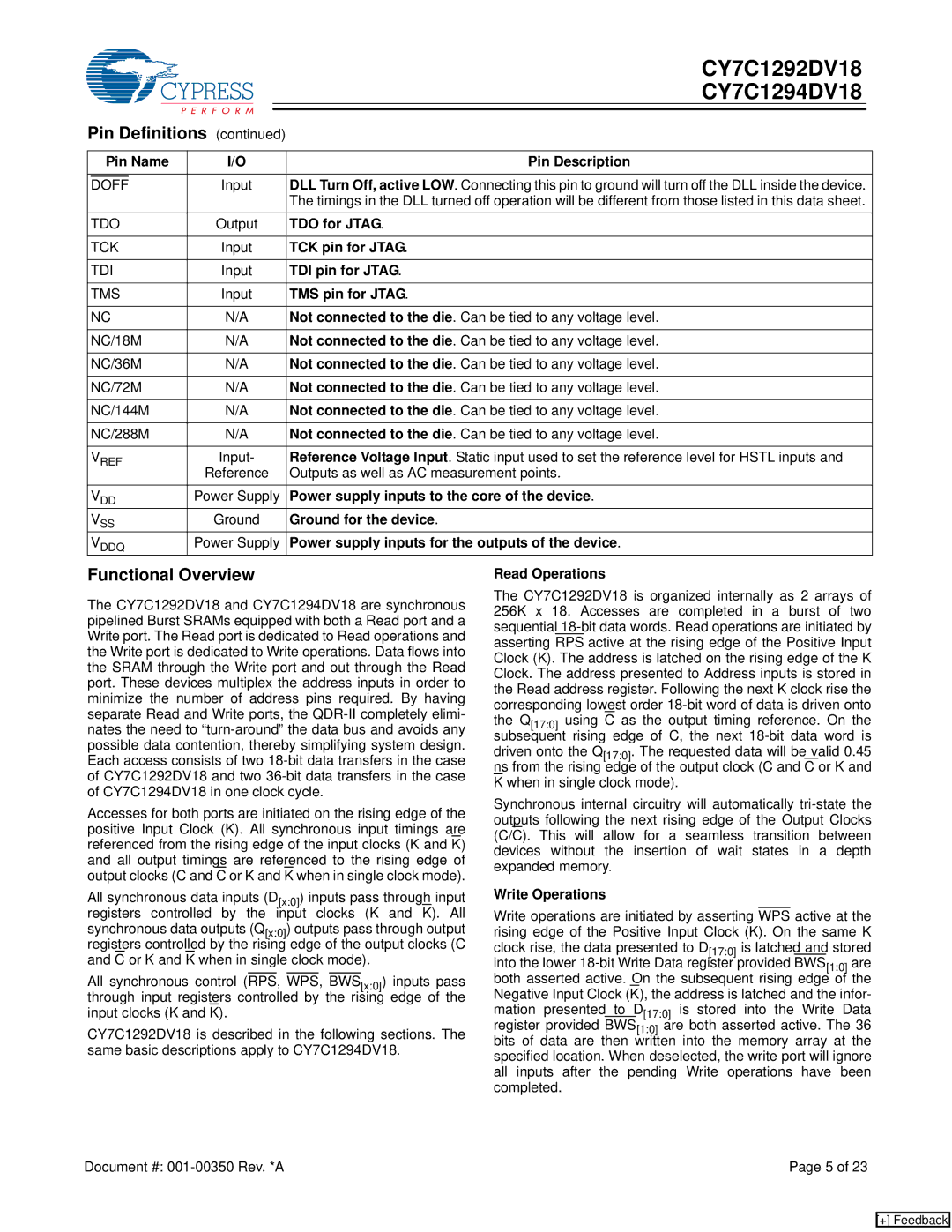

Pin Definitions (continued) |

|

| ||||||

|

|

|

|

| ||||

| Pin Name | I/O | Pin Description |

| ||||

|

|

|

|

|

| |||

|

|

| Input | DLL Turn Off, active LOW. Connecting this pin to ground will turn off the DLL inside the device. |

| |||

| DOFF |

| ||||||

|

|

|

|

|

|

| The timings in the DLL turned off operation will be different from those listed in this data sheet. |

|

| TDO | Output | TDO for JTAG. |

| ||||

|

|

|

|

| ||||

| TCK | Input | TCK pin for JTAG. |

| ||||

|

|

|

|

| ||||

| TDI | Input | TDI pin for JTAG. |

| ||||

|

|

|

|

| ||||

| TMS | Input | TMS pin for JTAG. |

| ||||

|

|

|

|

| ||||

| NC | N/A | Not connected to the die. Can be tied to any voltage level. |

| ||||

|

|

|

|

| ||||

| NC/18M | N/A | Not connected to the die. Can be tied to any voltage level. |

| ||||

|

|

|

| |||||

NC/36M | N/A | Not connected to the die. Can be tied to any voltage level. |

| |||||

|

|

|

| |||||

NC/72M | N/A | Not connected to the die. Can be tied to any voltage level. |

| |||||

|

|

|

| |||||

NC/144M | N/A | Not connected to the die. Can be tied to any voltage level. |

| |||||

|

|

|

| |||||

NC/288M | N/A | Not connected to the die. Can be tied to any voltage level. |

| |||||

|

|

|

| |||||

VREF | Input- | Reference Voltage Input. Static input used to set the reference level for HSTL inputs and |

| |||||

|

|

|

| Reference | Outputs as well as AC measurement points. |

| ||

| VDD | Power Supply | Power supply inputs to the core of the device. |

| ||||

| VSS | Ground | Ground for the device. |

| ||||

| VDDQ | Power Supply | Power supply inputs for the outputs of the device. |

| ||||

Functional Overview

The CY7C1292DV18 and CY7C1294DV18 are synchronous pipelined Burst SRAMs equipped with both a Read port and a Write port. The Read port is dedicated to Read operations and the Write port is dedicated to Write operations. Data flows into the SRAM through the Write port and out through the Read port. These devices multiplex the address inputs in order to minimize the number of address pins required. By having separate Read and Write ports, the

Accesses for both ports are initiated on the rising edge of the positive Input Clock (K). All synchronous input timings are referenced from the rising edge of the input clocks (K and K) and all output timings are referenced to the rising edge of output clocks (C and C or K and K when in single clock mode).

All synchronous data inputs (D[x:0]) inputs pass through input registers controlled by the input clocks (K and K). All synchronous data outputs (Q[x:0]) outputs pass through output registers controlled by the rising edge of the output clocks (C and C or K and K when in single clock mode).

All synchronous control (RPS, WPS, BWS[x:0]) inputs pass through input registers controlled by the rising edge of the input clocks (K and K).

CY7C1292DV18 is described in the following sections. The same basic descriptions apply to CY7C1294DV18.

Read Operations

The CY7C1292DV18 is organized internally as 2 arrays of 256K x 18. Accesses are completed in a burst of two sequential

Synchronous internal circuitry will automatically

Write Operations

Write operations are initiated by asserting WPS active at the rising edge of the Positive Input Clock (K). On the same K clock rise, the data presented to D[17:0] is latched and stored into the lower

Document #: | Page 5 of 23 |

[+] Feedback