CY7C1292DV18

CY7C1294DV18

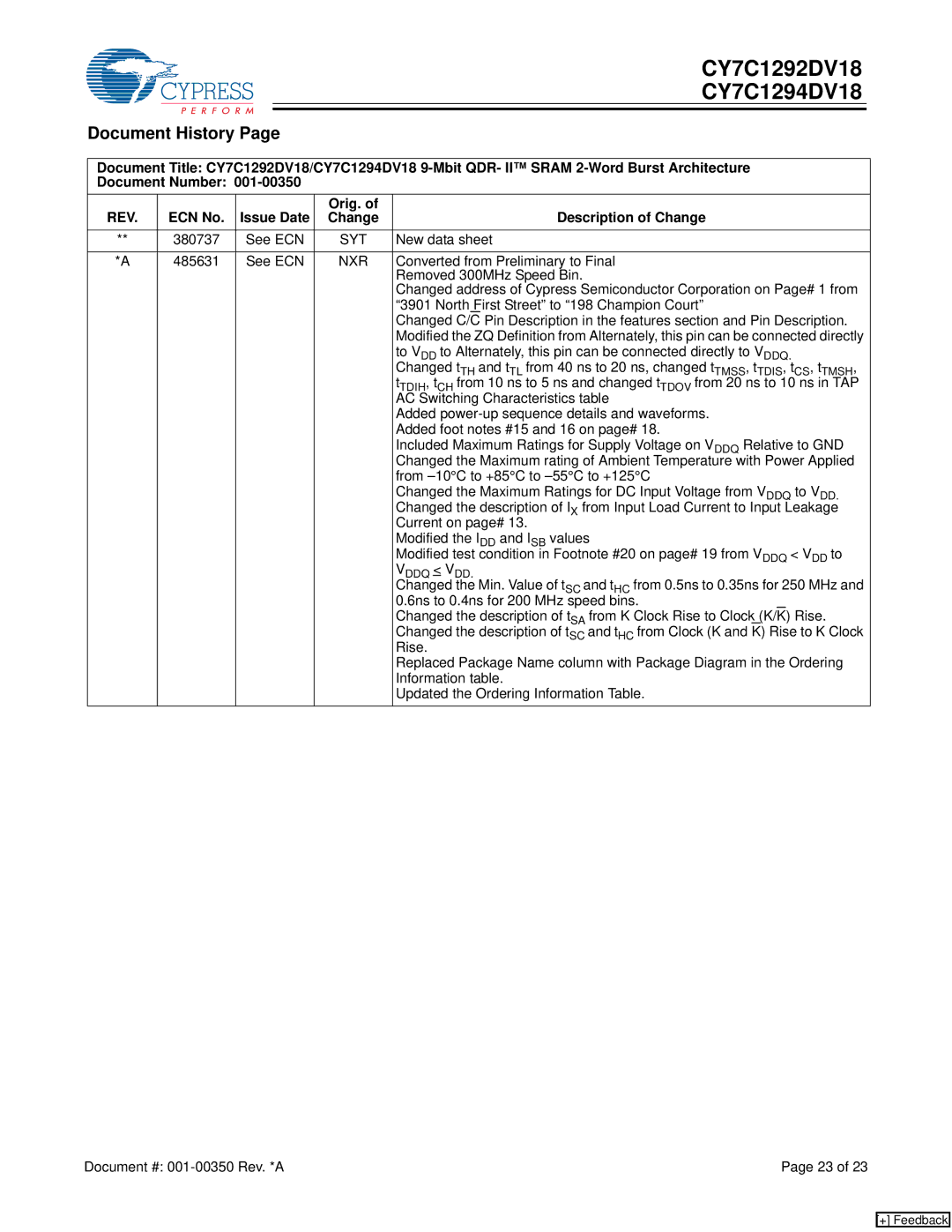

Document History Page

Document Title: CY7C1292DV18/CY7C1294DV18

Document Number:

REV. | ECN No. | Issue Date | Orig. of | Description of Change | ||||

Change | ||||||||

|

|

|

|

| ||||

** | 380737 | See ECN | SYT | New data sheet | ||||

|

|

|

|

| ||||

*A | 485631 | See ECN | NXR | Converted from Preliminary to Final | ||||

|

|

|

| Removed 300MHz Speed Bin. | ||||

|

|

|

| Changed address of Cypress Semiconductor Corporation on Page# 1 from | ||||

|

|

|

| “3901 North First Street” to “198 Champion Court” | ||||

|

|

|

| Changed C/C Pin Description in the features section and Pin Description. | ||||

|

|

|

| Modified the ZQ Definition from Alternately, this pin can be connected directly | ||||

|

|

|

| to VDD to Alternately, this pin can be connected directly to VDDQ. | ||||

|

|

|

| Changed tTH and tTL from 40 ns to 20 ns, changed tTMSS, tTDIS, tCS, tTMSH, | ||||

|

|

|

| tTDIH, tCH from 10 ns to 5 ns and changed tTDOV from 20 ns to 10 ns in TAP | ||||

|

|

|

| AC Switching Characteristics table | ||||

|

|

|

| Added | ||||

|

|

|

| Added foot notes #15 and 16 on page# 18. | ||||

|

|

|

| Included Maximum Ratings for Supply Voltage on VDDQ Relative to GND | ||||

|

|

|

| Changed the Maximum rating of Ambient Temperature with Power Applied | ||||

|

|

|

| from | ||||

|

|

|

| Changed the Maximum Ratings for DC Input Voltage from VDDQ to VDD. | ||||

|

|

|

| Changed the description of IX from Input Load Current to Input Leakage | ||||

|

|

|

| Current on page# 13. | ||||

|

|

|

| Modified the IDD and ISB values | ||||

|

|

|

| Modified test condition in Footnote #20 on page# 19 from VDDQ < VDD to | ||||

|

|

|

| VDDQ < VDD. | ||||

|

|

|

| Changed the Min. Value of tSC and tHC from 0.5ns to 0.35ns for 250 MHz and | ||||

|

|

|

| 0.6ns to 0.4ns for 200 MHz speed bins. |

|

| ||

|

|

|

| Changed the description of tSA from K Clock Rise to Clock |

| (K/K) | Rise. | |

|

|

|

| Changed the description of tSC and tHC from Clock (K and K) Rise to K Clock | ||||

|

|

|

| Rise. | ||||

|

|

|

| Replaced Package Name column with Package Diagram in the Ordering | ||||

|

|

|

| Information table. | ||||

|

|

|

| Updated the Ordering Information Table. | ||||

Document #: | Page 23 of 23 |

[+] Feedback