CY7C1310BV18, CY7C1910BV18 CY7C1312BV18, CY7C1314BV18

Programmable Impedance

An external resistor, RQ, must be connected between the ZQ pin on the SRAM and VSS to allow the SRAM to adjust its output driver impedance. The value of RQ must be 5x the value of the intended line impedance driven by the SRAM. The allowable range of RQ to guarantee impedance matching with a tolerance of ±15% is between 175Ω and 350Ω, with VDDQ = 1.5V. The output impedance is adjusted every 1024 cycles upon power up to account for drifts in supply voltage and temperature.

Echo Clocks

Echo clocks are provided on the

synchronized to the output clock (C/C) of the

DLL

These chips use a Delay Lock Loop (DLL) that is designed to function between 120 MHz and the specified maximum clock frequency. During power up, when the DOFF is tied HIGH, the DLL is locked after 1024 cycles of stable clock. The DLL can also be reset by slowing or stopping the input clock K and K for a minimum of 30 ns. However, it is not necessary to reset the DLL to lock to the desired frequency. The DLL automatically locks 1024 clock cycles after a stable clock is presented. The DLL may be disabled by applying ground to the DOFF pin. For information refer to the application note AN5062, DLL Considerations in QDRII/DDRII/QDRII+/DDRII+.

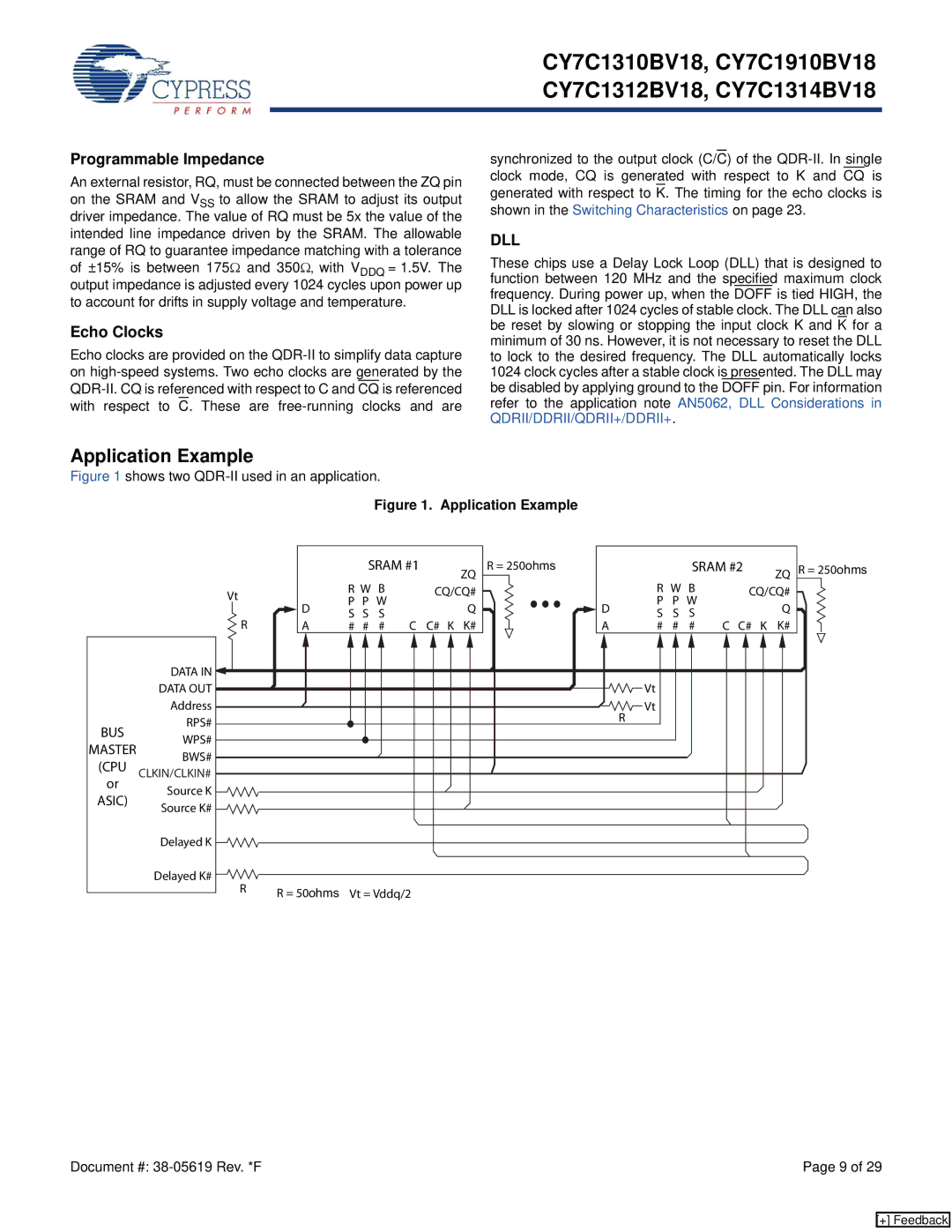

Application Example |

|

|

|

|

|

|

|

|

|

| |

Figure 1 shows two |

|

|

|

|

|

|

|

| |||

|

|

| Figure 1. Application Example |

|

|

|

|

| |||

|

|

| SRAM #1 | ZQ | R = 250ohms |

| SRAM #2 | ZQ | R = 250ohms | ||

| Vt |

| R W B |

| CQ/CQ# |

| R W B |

| CQ/CQ# |

| |

| D | P P W |

| Q | D | P | P W |

| Q |

| |

|

|

|

|

| |||||||

|

| S S S |

| S | S S |

|

| ||||

| R |

|

|

|

|

|

|

| |||

| A | # # # | C C# K K# | A | # # # | C C# K K# |

| ||||

| DATA IN |

|

|

|

|

|

|

|

|

|

|

| DATA OUT |

|

|

|

|

| Vt |

|

|

|

|

| Address |

|

|

|

|

| Vt |

|

|

|

|

BUS | RPS# |

|

|

|

|

| R |

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

WPS# |

|

|

|

|

|

|

|

|

|

| |

MASTER |

|

|

|

|

|

|

|

|

|

| |

BWS# |

|

|

|

|

|

|

|

|

|

| |

(CPU |

|

|

|

|

|

|

|

|

|

| |

CLKIN/CLKIN# |

|

|

|

|

|

|

|

|

|

| |

or | Source K |

|

|

|

|

|

|

|

|

|

|

ASIC) |

|

|

|

|

|

|

|

|

|

| |

Source K# |

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

| |

| Delayed K |

|

|

|

|

|

|

|

|

|

|

| Delayed K# |

|

|

|

|

|

|

|

|

|

|

| R | R = 50ohms | Vt = Vddq/2 |

|

|

|

|

|

|

| |

Document #: | Page 9 of 29 |

[+] Feedback