CY7C1339G

4-Mbit (128K x 32) Pipelined Sync SRAM

Features

•Registered inputs and outputs for pipelined operation

•128K × 32 common I/O architecture

•3.3V core power supply (VDD)

•2.5V/3.3V I/O power supply (VDDQ)

•Fast

— 2.6 ns (for

•Provide

•

•Separate processor and controller address strobes

•Synchronous

•Asynchronous output enable

•Available in

•“ZZ” Sleep Mode Option

Functional Description[1]

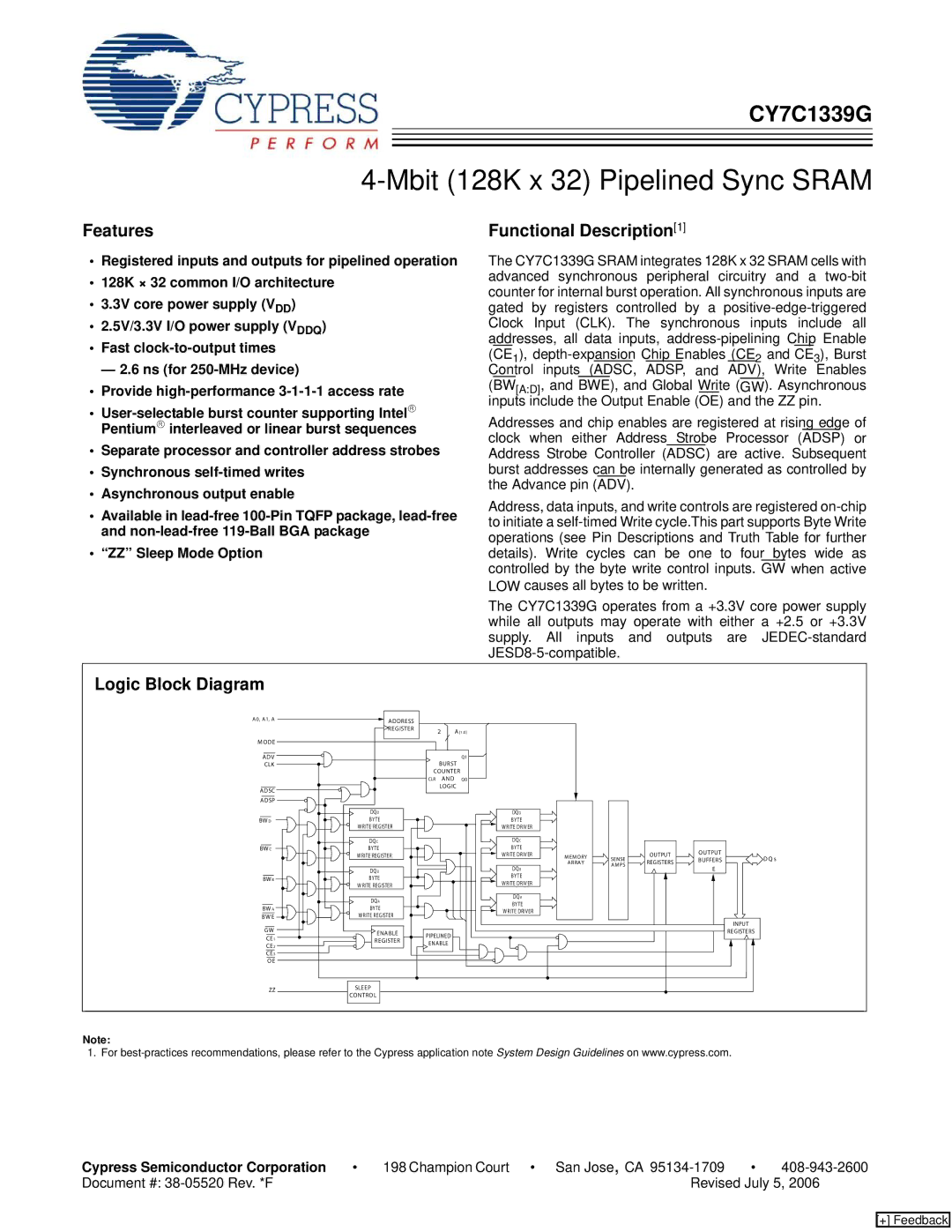

The CY7C1339G SRAM integrates 128K x 32 SRAM cells with advanced synchronous peripheral circuitry and a

Addresses and chip enables are registered at rising edge of clock when either Address Strobe Processor (ADSP) or Address Strobe Controller (ADSC) are active. Subsequent burst addresses can be internally generated as controlled by the Advance pin (ADV).

Address, data inputs, and write controls are registered

The CY7C1339G operates from a +3.3V core power supply while all outputs may operate with either a +2.5 or +3.3V supply. All inputs and outputs are

Logic Block Diagram

A 0, A 1, A

M O DE

A DV

CLK

A DSC

A DSP

BW D

BW C

BW B

B W A

B W E

G W

CE 1

CE 2

CE 3

O E

ZZ

A DDR E SS |

|

|

|

|

|

|

|

|

R E G ISTE R |

| 2 | A [1: 0] |

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

| Q 1 |

|

|

|

|

|

|

| B U R ST |

|

|

|

|

| |

| CO U N TE R |

|

|

|

|

| ||

| CLR | A N D | Q 0 |

|

|

|

|

|

|

| LO G IC |

|

|

|

|

| |

DQ D |

|

| DQ D |

|

|

|

|

|

BY TE |

|

| BY TE |

|

|

|

|

|

W RITE REGISTER |

|

| W RITE DRIV ER |

|

|

|

|

|

DQ C |

|

| DQ C |

|

|

|

|

|

BY TE |

|

| BY TE |

|

|

| O U TPU T |

|

W RITE REGISTER |

|

| W RITE DRIV ER | M E M O R Y |

| O U TPU T | D Q s | |

|

| SE N SE | B U FFE R S | |||||

|

|

|

| A R R A Y | R EG ISTER S | |||

|

|

| DQ B | A M PS |

|

| ||

|

|

|

|

| E |

| ||

DQ B |

|

|

|

|

|

| ||

BY TE |

|

| BY TE |

|

|

|

|

|

|

| W RITE DRIV ER |

|

|

|

|

| |

W RITE REGISTER |

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

| |

DQ A |

|

| DQ A |

|

|

|

|

|

|

| BY TE |

|

|

|

|

| |

BY TE |

|

|

|

|

|

|

| |

|

| W RITE DRIV ER |

|

|

|

|

| |

W RITE REGISTER |

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

| INPU T |

E N A B LE | PIPELINED |

|

|

|

|

| R EG ISTER S | |

|

|

|

|

|

| |||

R E G ISTE R |

|

|

|

|

|

| ||

ENA BLE |

|

|

|

|

|

| ||

|

|

|

|

|

|

| ||

SLE E P |

|

|

|

|

|

|

|

|

CO N TR O L |

|

|

|

|

|

|

|

|

Note:

1. For

Cypress Semiconductor Corporation | • | 198 Champion Court • San Jose, CA | • | |

Document #: |

| Revised July 5, 2006 | ||

[+] Feedback