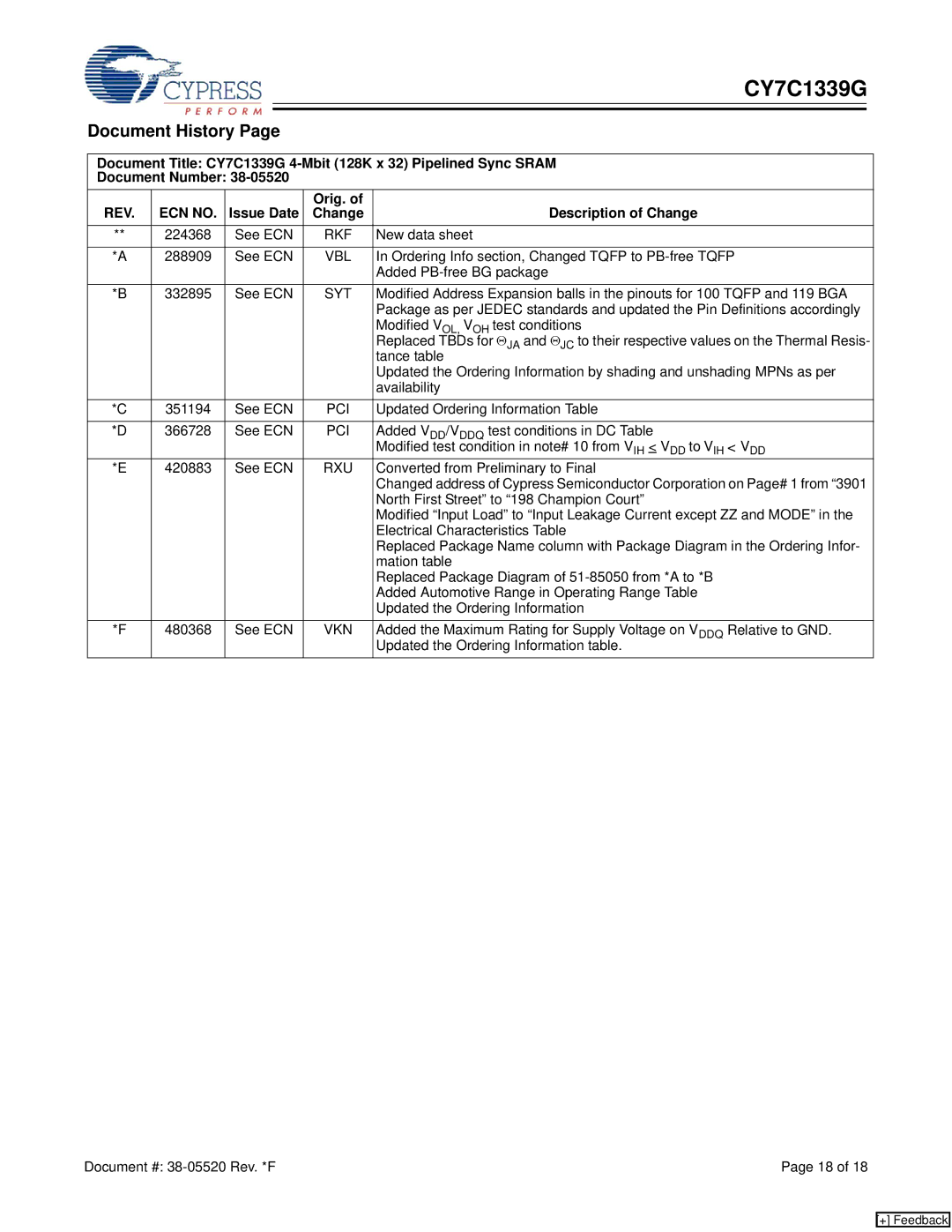

CY7C1339G

Document History Page

Document Title: CY7C1339G

Document Number:

REV. | ECN NO. | Issue Date | Orig. of | Description of Change |

Change | ||||

|

|

|

|

|

** | 224368 | See ECN | RKF | New data sheet |

|

|

|

|

|

*A | 288909 | See ECN | VBL | In Ordering Info section, Changed TQFP to |

|

|

|

| Added |

*B | 332895 | See ECN | SYT | Modified Address Expansion balls in the pinouts for 100 TQFP and 119 BGA |

|

|

|

| Package as per JEDEC standards and updated the Pin Definitions accordingly |

|

|

|

| Modified VOL, VOH test conditions |

|

|

|

| Replaced TBDs for ΘJA and ΘJC to their respective values on the Thermal Resis- |

|

|

|

| tance table |

|

|

|

| Updated the Ordering Information by shading and unshading MPNs as per |

|

|

|

| availability |

*C | 351194 | See ECN | PCI | Updated Ordering Information Table |

|

|

|

|

|

*D | 366728 | See ECN | PCI | Added VDD/VDDQ test conditions in DC Table |

|

|

|

| Modified test condition in note# 10 from VIH < VDD to VIH < VDD |

*E | 420883 | See ECN | RXU | Converted from Preliminary to Final |

|

|

|

| Changed address of Cypress Semiconductor Corporation on Page# 1 from “3901 |

|

|

|

| North First Street” to “198 Champion Court” |

|

|

|

| Modified “Input Load” to “Input Leakage Current except ZZ and MODE” in the |

|

|

|

| Electrical Characteristics Table |

|

|

|

| Replaced Package Name column with Package Diagram in the Ordering Infor- |

|

|

|

| mation table |

|

|

|

| Replaced Package Diagram of |

|

|

|

| Added Automotive Range in Operating Range Table |

|

|

|

| Updated the Ordering Information |

*F | 480368 | See ECN | VKN | Added the Maximum Rating for Supply Voltage on VDDQ Relative to GND. |

|

|

|

| Updated the Ordering Information table. |

Document #: | Page 18 of 18 |

[+] Feedback