CY7C1354C

CY7C1356C

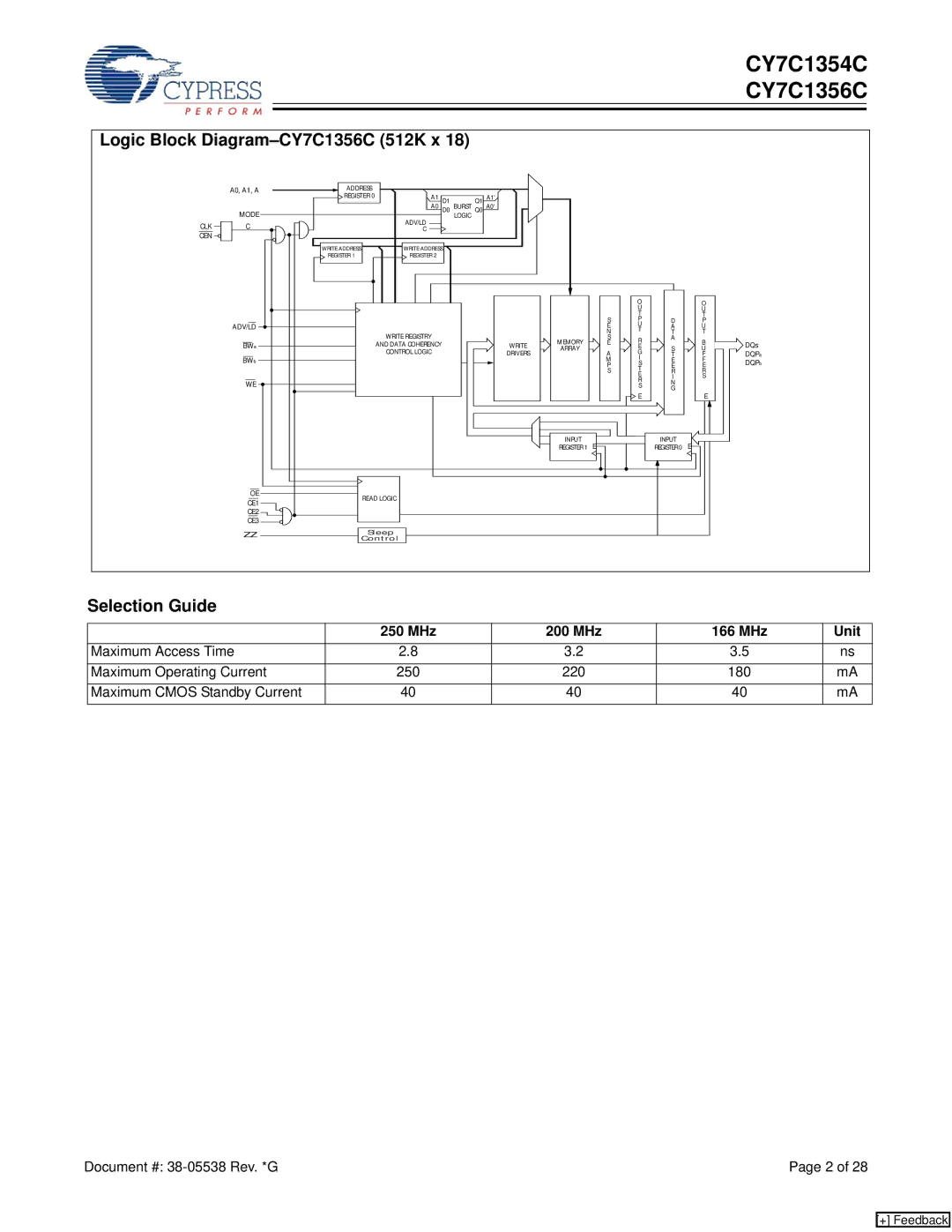

Logic Block |

|

|

|

|

|

| |||||

| A0, A1, A | ADDRESS |

|

|

|

|

|

|

|

| |

|

| REGISTER 0 | A1 | D1 | Q1 A1' |

|

|

|

|

| |

|

|

|

|

|

|

|

|

| |||

| MODE |

|

| A0 | D0 BURST Q0 A0' |

|

|

|

|

| |

|

|

| ADV/LD | LOGIC |

|

|

|

|

|

| |

CLK | C |

|

|

|

|

|

|

|

|

| |

|

| C |

|

|

|

|

|

|

| ||

CEN |

|

|

|

|

|

|

|

|

|

|

|

|

| WRITE ADDRESS |

| WRITE ADDRESS |

|

|

|

|

|

| |

|

| REGISTER 1 |

| REGISTER 2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| O |

| O |

|

|

|

|

|

|

|

|

| U |

| U |

|

|

|

|

|

|

|

|

| T |

| T |

| ADV/LD |

|

|

|

|

|

| S | P | D | P |

|

|

|

|

|

|

| E | U | A | U | |

|

|

|

| WRITE REGISTRY |

|

|

| N | T | T | T |

|

|

|

|

|

| MEMORY | S | R | A | B | |

| BWa |

|

| AND DATA COHERENCY |

| WRITE | E |

| |||

|

|

|

| ARRAY |

| E | S | U | |||

|

|

|

| CONTROL LOGIC |

| DRIVERS | A | G | |||

|

|

|

|

|

| T | F | ||||

| BWb |

|

|

|

|

|

| M | I | E | F |

|

|

|

|

|

|

|

| P | S | E | E |

|

|

|

|

|

|

|

| S | T | R | R |

|

|

|

|

|

|

|

|

| E | I | S |

| WE |

|

|

|

|

|

|

| R | N |

|

|

|

|

|

|

|

|

| S |

| ||

|

|

|

|

|

|

|

|

|

| G |

|

|

|

|

|

|

|

|

|

| E |

| E |

|

|

|

|

|

|

| INPUT | E |

| INPUT | E |

|

|

|

|

|

|

| REGISTER 1 |

| REGISTER 0 | ||

| OE |

| READ LOGIC |

|

|

|

|

|

|

| |

| CE1 |

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

| |

| CE2 |

|

|

|

|

|

|

|

|

|

|

| CE3 |

|

|

|

|

|

|

|

|

|

|

| ZZ |

| Sleep |

|

|

|

|

|

|

| |

|

|

| Control |

|

|

|

|

|

|

| |

DQs DQPa DQPb

Selection Guide

| 250 MHz | 200 MHz | 166 MHz | Unit |

Maximum Access Time | 2.8 | 3.2 | 3.5 | ns |

Maximum Operating Current | 250 | 220 | 180 | mA |

Maximum CMOS Standby Current | 40 | 40 | 40 | mA |

Document #: | Page 2 of 28 |

[+] Feedback