CY7C1371D

CY7C1373D

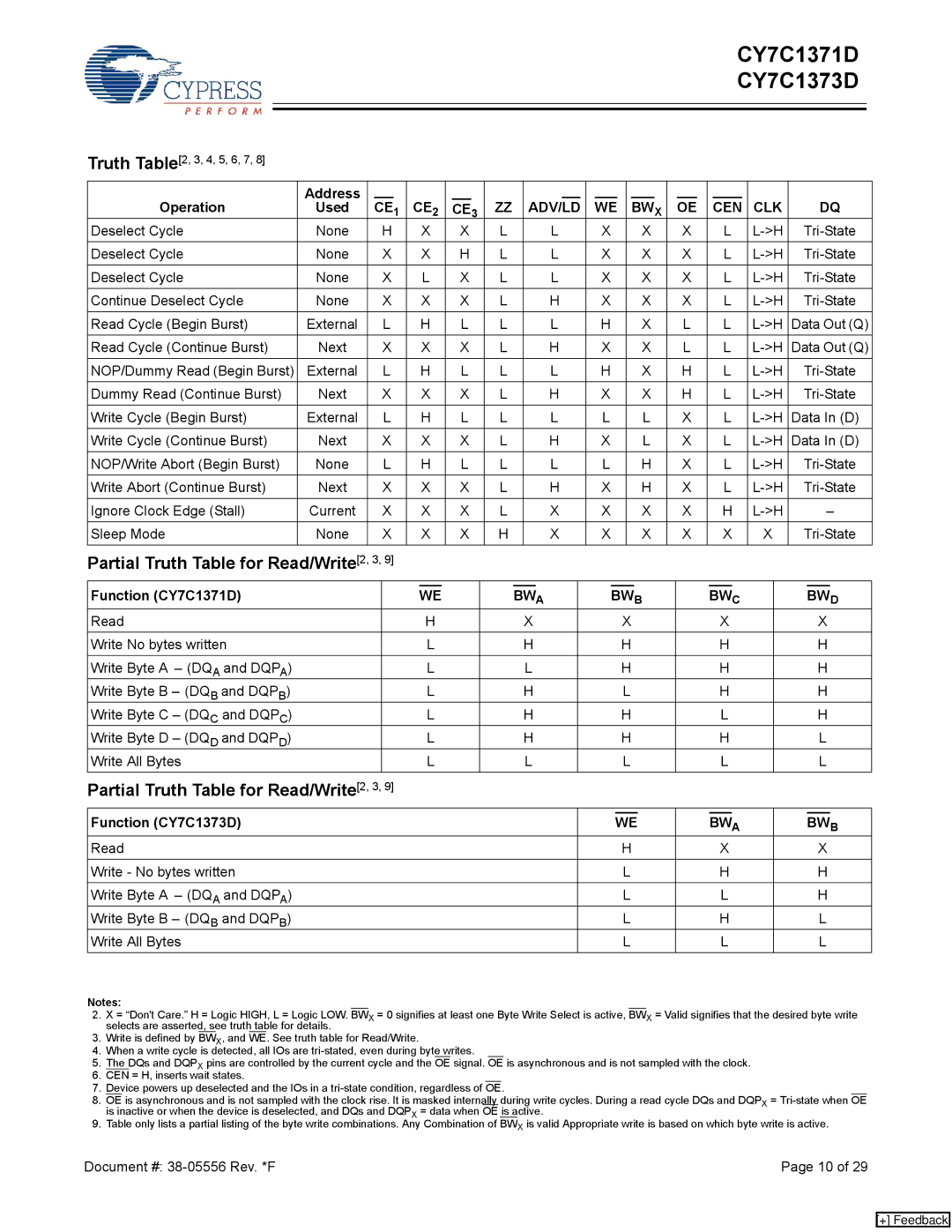

Truth Table[2, 3, 4, 5, 6, 7, 8]

| Address |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Operation | Used |

| CE | 1 | CE2 |

| CE | 3 |

| ZZ |

| ADV/LD |

|

| WE |

|

| BWX |

| OE |

|

|

| CEN | CLK |

| DQ | ||||||||||||||||

Deselect Cycle | None |

|

| H |

| X |

| X | L |

|

| L |

| X |

|

|

|

| X |

| X |

|

|

| L | ||||||||||||||||||

Deselect Cycle | None |

|

| X |

| X |

| H | L |

|

| L |

| X |

|

|

|

| X |

| X |

|

|

| L | ||||||||||||||||||

Deselect Cycle | None |

|

| X |

| L |

| X | L |

|

| L |

| X |

|

|

|

| X |

| X |

|

|

| L | ||||||||||||||||||

Continue Deselect Cycle | None |

|

| X |

| X |

| X | L |

|

| H |

| X |

|

|

|

| X |

| X |

|

|

| L | ||||||||||||||||||

Read Cycle (Begin Burst) | External |

|

| L |

| H |

| L | L |

|

| L |

| H |

|

|

|

| X |

| L |

|

|

| L | Data Out (Q) | |||||||||||||||||

Read Cycle (Continue Burst) | Next |

|

| X |

| X |

| X | L |

|

| H |

| X |

|

|

|

| X |

| L |

|

|

| L | Data Out (Q) | |||||||||||||||||

NOP/Dummy Read (Begin Burst) | External |

|

| L |

| H |

| L | L |

|

| L |

| H |

|

|

|

| X |

| H |

|

|

| L | ||||||||||||||||||

Dummy Read (Continue Burst) | Next |

|

| X |

| X |

| X | L |

|

| H |

| X |

|

|

|

| X |

| H |

|

|

| L | ||||||||||||||||||

Write Cycle (Begin Burst) | External |

|

| L |

| H |

| L | L |

|

| L |

| L |

|

|

|

| L |

| X |

|

|

| L | Data In (D) | |||||||||||||||||

Write Cycle (Continue Burst) | Next |

|

| X |

| X |

| X | L |

|

| H |

| X |

|

|

|

| L |

| X |

|

|

| L | Data In (D) | |||||||||||||||||

NOP/Write Abort (Begin Burst) | None |

|

| L |

| H |

| L | L |

|

| L |

| L |

|

|

|

| H |

| X |

|

|

| L | ||||||||||||||||||

Write Abort (Continue Burst) | Next |

|

| X |

| X |

| X | L |

|

| H |

| X |

|

|

|

| H |

| X |

|

|

| L | ||||||||||||||||||

Ignore Clock Edge (Stall) | Current |

|

| X |

| X |

| X | L |

|

| X |

| X |

|

|

|

| X |

| X |

|

|

| H |

| – | ||||||||||||||||

Sleep Mode | None |

|

| X |

| X |

| X | H |

|

| X |

| X |

|

|

|

| X |

| X |

|

|

| X | X | |||||||||||||||||

Partial Truth Table for Read/Write[2, 3, 9] |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

Function (CY7C1371D) |

|

|

|

|

|

| WE |

|

|

|

|

|

| BW | A |

|

| BW | B |

|

| BW | C |

|

|

| BW | D | |||||||||||||||

Read |

|

|

|

|

|

| H |

|

|

|

|

| X |

|

|

|

|

|

| X |

|

|

|

| X |

|

|

| X | ||||||||||||||

Write No bytes written |

|

|

|

|

|

| L |

|

|

|

|

| H |

|

|

|

|

|

| H |

|

|

|

| H |

|

|

| H | ||||||||||||||

Write Byte A – (DQA and DQPA) |

|

|

|

|

|

| L |

|

|

|

|

| L |

|

|

|

|

|

| H |

|

|

|

| H |

|

|

| H | ||||||||||||||

Write Byte B – (DQB and DQPB) |

|

|

|

|

|

| L |

|

|

|

|

| H |

|

|

|

|

|

| L |

|

|

|

| H |

|

|

| H | ||||||||||||||

Write Byte C – (DQC and DQPC) |

|

|

|

|

|

| L |

|

|

|

|

| H |

|

|

|

|

|

| H |

|

|

|

| L |

|

|

| H | ||||||||||||||

Write Byte D – (DQD and DQPD) |

|

|

|

|

|

| L |

|

|

|

|

| H |

|

|

|

|

|

| H |

|

|

|

| H |

|

|

| L | ||||||||||||||

Write All Bytes |

|

|

|

|

|

| L |

|

|

|

|

| L |

|

|

|

|

|

| L |

|

|

|

| L |

|

|

| L | ||||||||||||||

Partial Truth Table for Read/Write[2, 3, 9] |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

Function (CY7C1373D) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| WE |

|

|

|

|

| BW | A |

|

|

| BW | B | ||||||||

Read |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| H |

|

|

|

| X |

|

|

| X | ||||||||||

Write - No bytes written |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| L |

|

|

|

| H |

|

|

| H | ||||||||||

Write Byte A – (DQA and DQPA) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| L |

|

|

|

| L |

|

|

| H | ||||||||||

Write Byte B – (DQB and DQPB) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| L |

|

|

|

| H |

|

|

| L | ||||||||||

Write All Bytes |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| L |

|

|

|

| L |

|

|

| L | ||||||||||

Notes:

2.X = “Don't Care.” H = Logic HIGH, L = Logic LOW. BWX = 0 signifies at least one Byte Write Select is active, BWX = Valid signifies that the desired byte write selects are asserted, see truth table for details.

3.Write is defined by BWX, and WE. See truth table for Read/Write.

4.When a write cycle is detected, all IOs are

5.The DQs and DQPX pins are controlled by the current cycle and the OE signal. OE is asynchronous and is not sampled with the clock.

6.CEN = H, inserts wait states.

7.Device powers up deselected and the IOs in a

8.OE is asynchronous and is not sampled with the clock rise. It is masked internally during write cycles. During a read cycle DQs and DQPX =

9.Table only lists a partial listing of the byte write combinations. Any Combination of BWX is valid Appropriate write is based on which byte write is active.

Document #: | Page 10 of 29 |

[+] Feedback